XC2C256-7TQ144C CPLD: PINOUT, Funkcie, programovanie a sprievodca údajmi

V tejto príručke sa jasne pozriete na XC2C256-7TQ144C, nízkoenergetickú CPLD z rodiny Coolrunner-II Xilinx (teraz AMD).Dozviete sa o jeho konfigurácii PIN, CAD modeloch a hlavných funkciách, ako sú logická kapacita, možnosti I/O, podporu napätia a funkcie úspory energie.Prejdeme tiež jeho architektúrou, krivkou I/V a špecifikáciami, po ktorých nasledujú aplikácie, podobné časti, programovacie kroky, výhody a nevýhody, detaily obalov a informácie o výrobcovi, aby ste presne pochopili, ako toto zariadenie zapadá do vašich projektov.Katalóg

Čo je XC2C256-7TQ144C?

Ten XC2C256-7TQ144C je nízkoenergetický CPLD (komplexné programovateľné logické zariadenie) z rodiny Coolrunner-II spoločnosti Xilinx, ktorá je teraz súčasťou AMD.Má 256 makrocellov a je dodávaný v balení 144-kolík TQFP určených pre rýchlu, deterministickú prevádzku s minimálnou spotrebou energie.Pracuje sa na jadre 1,8 V a ponúka spoľahlivý výkon v kompaktnom formálnom faktore a je vhodný pre návrhy, ktoré si vyžadujú okamžitú schopnosť a efektívnu logickú implementáciu.V rámci všestrannej série Coolrunner-II má úžitok z osvedčenej architektúry a širokej kompatibility dizajnu.

Hľadáte XC2C256-7TQ144C?Kontaktujte nás a skontrolujte aktuálne zásoby, dodací čas a ceny.

XC2C256-7TQ144C Schéma

Schéma Pin-Out XC2C256-7TQ144C ukazuje, ako je usporiadaných 144 kolíkov pre funkcie výkonu, zeme, JTAG a používateľom, ktoré sú prevoditeľné I/O.Väčšina kolíkov je I/O, ktoré možno nakonfigurovať ako vstupy alebo výstupy a sú rovnomerne distribuované na podporu flexibilného smerovania.PINS VCC, VCCIO1, VCCIO2, VAUX a GND sa umiestnia okolo balíka, aby sa zabezpečilo stabilné rozdelenie energie a viac možností I/O napätia.PINS JTAG (TDI, TDO, TMS, TCK) sú zoskupené pre ľahké programovanie a testovanie systému v systéme.

XC2C256-7TQ144C CAD modely

Symbol XC2C256-7TQ144C

XC2C256-7TQ144C Footprint

XC2C256-7TQ144C 3D model

XC2C256-7TQ144C Vlastnosti

• Typ zariadenia a rodina

XC2C256-7TQ144C je komplexné programovateľné logické zariadenie (CPLD), ktoré patrí do rodiny CoolRunner-II vyvinutá spoločnosťou XilInx (teraz AMD).Je navrhnutý na nízku spotrebu energie pri udržiavaní rýchleho a deterministického logického výkonu, vďaka čomu je ideálny pre aplikácie riadenia a rozhrania.

• Logická kapacita

Toto zariadenie obsahuje 256 makrocellov, ktoré sú programovateľnými logickými zdrojmi v CPLD.Tieto makrocelly môžu byť nakonfigurované na implementáciu rôznych kombinovaných a sekvenčných logických funkcií, čo dáva miernu kapacitu na riadenie, logiku lepidla a rozhrania zbernice.

• Logické bloky (funkčné bloky)

Integruje 16 funkčných blokov, ktoré organizujú a spravujú skupiny makrocellov.Každý blok poskytuje miestne prepojené a produktové zdroje, čo umožňuje flexibilnú logickú implementáciu a efektívne smerovanie v zariadení.

• Užívateľ I/O Pins

XC2C256-7TQ144C ponúka až 118 používateľských konfigurovateľných I/O kolíkov v balíku TQFP-144.Tento vysoký počet kolíkov umožňuje zariadeniu prepojiť sa s viacerými subsystémami súčasne, takže je vhodné pre zložité vzory na úrovni dosky.

• Napätie jadra (VCC)

Jadro funguje pri nominálnom rozmedzí 1,8 V (1,7 V až 1,9 V), čo pomáha znižovať spotrebu energie v porovnaní so staršími 5 V CPLD.Toto spodné napätie je užitočné v moderných digitálnych systémoch zmiešaného napätia.

• Podpora I/O viacerých napätí

I/O banky podporujú viac štandardov napätia vrátane 1,5 V, 1,8 V, 2,5 V a 3,3 V. Táto flexibilita umožňuje CPLD priamo rozhranie s komponentmi pracujúcimi pri rôznych úrovniach napätia bez externých úrovní.

• Vysokorýchlostná prevádzka

S typickým oneskorením šírenia pin-to-pin okolo 5,7 ns (rýchlostný stupeň „-7“) zariadenie poskytuje rýchly a deterministický výkon.Vďaka tomu je vhodné pre časovanie kritických aplikácií, ako je dekódovanie adresy, rozhodcovské konanie a kontrola zbernice.

• Nízka spotreba energie

Séria CoolRunner-II je známa extrémne nízkymi pohotovostnými prúdmi, často v rozsahu mikropodnikov.Tento nízky statický výkon v kombinácii s dynamickými funkciami úspory napájania umožňuje efektívne používanie XC2C256-7TQ144C v systémoch napájaných z batérie alebo neustále.

• Technológia datagate

Táto funkcia umožňuje zabrániť nepoužívaným vstupom, čím zabráni zbytočnému prepínaniu a znižovaniu dynamickej spotreby energie.Je to cenné v aplikáciách, kde sú určité signály po dlhú dobu neaktívne.

• Programovanie JTAG v systéme

Zariadenie podporuje IEEE 1149.1 (JTAG) a IEEE 1532 pre programovanie v systéme.To znamená, že CPLD môže byť nakonfigurovaný, testovaný a preprogramovaný bez toho, aby bol odstránený z dosky, zjednodušenie vývoja a aktualizácií.

• Advanced Clocking Structure

XC2C256-7TQ144C obsahuje viac globálnych hodín, rozdeľovače hodín a dvojdielne spustené registre.Poskytuje tiež globálne set/resetovanie a lokálne prekladanie na makrocelku, čo dáva flexibilné riadenie na načasovanie a synchronizáciu.

• Vstupy Schmitt-Trigger

Vybrané vstupné kolíky môžu byť nakonfigurované ako spúšťače Schmitt na zlepšenie imunity šumu.Je to užitočné na manipuláciu s pomalými alebo hlučnými vstupnými signálmi bez pridania externých kondicionovacích obvodov.

• Flexibilné výstupné funkcie

Výstupy podporujú operáciu s tromi štátmi, riadenie rýchlosti smitého, zadržiavanie zbernice, konfigurácie s otvoreným odtokom a voliteľné vytiahnutie.Tieto možnosti uľahčujú prispôsobenie CPLD rôznym štandardom zbernice a podmienkam externého zaťaženia.

• Advanced Interconnect Matrix (AIM)

Pokročilá prepojovacia matica efektívne spája funkčné bloky a poskytuje úplné smerovanie produktu cez zariadenie.To zlepšuje flexibilitu logického umiestnenia a pomáha udržiavať predvídateľný výkon načasovania.

CoolRunner-II CPLD Architektúra

CoolRunner-II CPLD architektúra XC2C256-7TQ144C je postavená okolo funkčných blokov, I/O blokov a pokročilej prepojenej matice (AIM).Každý blok funkcie obsahuje makrocelly a programovateľné logické pole (PLA), ktoré implementujú logiku definovanú používateľom, zatiaľ čo AIM efektívne smeruje signály medzi blokmi.I/O blokuje rozhranie internej logiky s externými kolíkmi a špecializované programovanie a testovanie obvodov JTAG a BSC/ISP podporujú v systéme.Táto štruktúrovaná a vzájomne prepojená architektúra umožňuje rýchly, deterministický výkon s nízkou spotrebou energie, vďaka čomu je ideálny pre riadenie, rozhranie a logiku lepidla v digitálnych systémoch.

Typická krivka I/V pre XC2C256

Typická krivka I/V pre XC2C256-7TQ144C ilustruje vzťah medzi výstupným napätím (VO) a výstupným prúdom (IO) pre rôzne vstupno-výstupné napätia (1,5 V, 1,8 V, 2,5 V a 3,3 V).Keď sa napájacie napätie zvyšuje, zariadenie môže získať alebo klesať vyššie prúdy skôr, ako výstupné napätie začne výrazne klesať.Toto správanie je dôležité pre pochopenie schopnosti pohonu CPLD pri prepojení s externými komponentmi, zabezpečenie úrovne signálu zostáva pri zaťažení platné.Mnohé z nich používajú túto krivku na výber vhodných vstupno-výstupných napätí a zabezpečenie spoľahlivej prevádzky v aplikáciách, ktoré vyžadujú konkrétne silné stránky riadenia prúdu.

XC2C256-7TQ144C Špecifikácie

|

Typ |

Parameter |

|

Výrobca |

Amd/xilinx |

|

Séria |

Coolrunner II |

|

Balenie |

Podnos |

|

Stav |

Zastaraný |

|

Programovateľný typ |

V systéme programovateľné |

|

Čas oneskorenia TPD (1) max |

6,7 ns |

|

Dodávka napätia - vnútorná |

1,7 V ~ 1,9 V |

|

Počet logických prvkov/blokov |

16 |

|

Počet makrocellov |

256 |

|

Počet brán |

6000 |

|

Počet I/O |

118 |

|

Prevádzková teplota |

0 ° C ~ 70 ° C (TA) |

|

Montáž |

Povrchová montáž |

|

Balenie |

144-lqfp

|

|

Balík dodávateľských zariadení |

144-TQFP (20 × 20) |

|

Základné číslo produktu |

XC2C256 |

XC2C256-7TQ144C Aplikácie

1. Logika lepidla a premostenie rozhrania

XC2C256-7TQ144C je ideálny na implementáciu logiky lepidla, ktorá spája a koordinuje signály medzi rôznymi digitálnymi komponentmi.Dokáže manipulovať s funkciami, ako je dekódovanie adries, arbitráž zbernice a preklad protokolu, čo umožňuje hladkú komunikáciu medzi mikrokontrolérmi, pamäťou, senzormi a inými periférnymi zariadeniami.Jeho predvídateľné načasovanie a rýchle oneskorenia pin-to-pin zaisťujú spoľahlivé rozhranie aj pri zložitých návrhoch dosiek.

2. Zariadenia s nízkym výkonom a batériou

Vďaka svojej technológii Fast Zero Power (FZP) a veľmi nízkym pohotovostným prúdom je tento CPLD veľmi vhodný pre prenosnú elektroniku poháňanú batériou.Môže zostať napájaný nepretržite a zároveň konzumovať minimálnu energiu, vďaka čomu je ideálny pre vždy na riadenie alebo monitorovanie obvodov.Využitie napájania môžete ďalej znížiť pomocou funkcií, ako je DataGate, ktoré minimalizujú dynamické prepínanie, keď sú vstupy neaktívne.

3. Logika riadenia a sekvenovanie

Zariadenie vyniká pri implementácii strojov s konečnými stavmi, riadenia načasovania a sekvencovania signálu požadovaných v mnohých zabudovaných systémoch.Jeho deterministická, neprchavá architektúra umožňuje, aby sa logika riadenia stala aktívnou bezprostredne po zapnutí bez oneskorení konfigurácie.Vďaka tomu je silnou voľbou pre resetovaciu logiku, obvody podania rúk a iné časovo kritické riadiace úlohy.

4. Podpora vloženého systému a periférna logika

V zabudovaných dizajnoch môže XC2C256-7TQ144C pôsobiť ako prispôsobiteľný podporný čip, ktorý implementuje špecializované rozhrania alebo rozširuje schopnosti mikrokontroléra.Dokáže spracovať komunikačné protokoly, ako sú SPI, I²C alebo UART, generujú výbery čipov alebo spravovať smerovanie prerušenia.Vyložením týchto funkcií z CPU zjednodušuje vývoj firmvéru a zlepšuje celkový výkon systému.

XC2C256-7TQ144C Podobné časti

|

Špecifikácia |

XC2C256-7TQ144C |

Xc2c256-7tq144i |

Xc2c256-7tqg144i |

XC2C256-7VQ100C |

XC2C256-7VQG100C |

XC2C256-6TQ144C |

|

Rodina zariadení |

Coolrunner-II CPLD |

Coolrunner-II CPLD |

Coolrunner-II CPLD |

Coolrunner-II CPLD |

Coolrunner-II CPLD |

Coolrunner-II CPLD |

|

Logická hustota (makrocelly) |

256 |

256 |

256 |

256 |

256 |

256 |

|

Typ balíka |

TQFP-144 |

TQFP-144 |

TQFP-144 (bez PB) |

VQFP-100 |

VQFP-100 (bez PB) |

TQFP-144 |

|

Rýchlosť |

-7 |

-7 |

-7 |

-7 |

-7 |

-6 (rýchlejšie) |

|

Teplotný rozsah |

Komerčné (0 - 70 ° C) |

Priemyselné (-40-85 ° C) |

Priemyselné (-40-85 ° C) |

Komerčné (0 - 70 ° C) |

Komerčné (0 - 70 ° C) |

Komerčné (0 - 70 ° C) |

|

Počet pinov I/O |

118 |

118 |

118 |

80 |

80 |

118 |

|

Napätie jadra (VCC) |

1,8 V |

1,8 V |

1,8 V |

1,8 V |

1,8 V |

1,8 V |

|

Podpora napätia I/O |

1,5 V - 3,3 V |

1,5 V - 3,3 V |

1,5 V - 3,3 V |

1,5 V - 3,3 V |

1,5 V - 3,3 V |

1,5 V - 3,3 V |

|

Súlad / bez PB |

Norma |

Norma |

PB bez PB / ROHS |

Norma |

PB bez PB / ROHS |

Norma |

|

Rozdiely |

Základná komerčná verzia |

Verzia priemyselnej teploty |

Priemyselná + verzia bez PB |

Menšie balenie, menej I/O |

Menšia verzia bez Pb |

Rýchlejšia načasovacia verzia |

XC2C256-7TQ144C Programovacie kroky

Programovanie XC2C256-7TQ144C je priamy proces, ktorý zahŕňa prípravu vášho dizajnu, generovanie programovacieho súboru a načítanie ho do CPLD prostredníctvom JTAG.Posledným sledovaním každého kroku môžete na doske zabezpečiť úspešnú konfiguráciu a správnu prevádzku zariadenia.

1. Návrh a syntetizujte

Začnete písaním logického dizajnu pomocou HDL (VHDL alebo Verilog) alebo schematického vstupu.Po dokončení návrhu spustíte proces syntézy, ktorý prevádza vašu logiku na vnútornú štruktúru makrocellov a prepojení zariadenia.Tento krok zaisťuje, že váš dizajn je kompatibilný s architektúrou XC2C256 a je pripravený na implementáciu.

2. Miesto a trasa / implementácia (montáž)

Ďalej vykonávate miesto a trasy, tiež známe ako montáž, ktoré priraďuje vašu syntetizovanú logiku skutočným fyzickým makrocelkám a smerovacím zdrojom vo vnútri CPLD.Nástroj kontroluje obmedzenia načasovania, rieši využitie zdrojov a optimalizuje cesty, aby splnil výkon vášho dizajnu.To zaisťuje, že obvod bude spoľahlivo spustený po naprogramovaní do zariadenia.

3. Vygenerujte programovací súbor

Po dokončení implementácie vygenerujete programovací súbor (formát BIT, JAM alebo SVF), ktorý obsahuje presné konfiguračné údaje pre zariadenie.Tento súbor predstavuje, ako je každý makrocel, interconnect a I/O nastavené na implementáciu vašej logiky.Pred prechodom na skutočné programovanie zariadení je potrebné mať tento súbor pripravený.

4. Programovanie JTAG / in-SYSTÉM

Nakoniec pripojíte zariadenie k počítaču pomocou programovacieho kábla JTAG a otvoríte nástroj Xilinx Impact Tool (alebo ekvivalent).Potom načítate vygenerovaný programovací súbor a stiahnete ho do XC2C256-7TQ144C prostredníctvom kolíkov JTAG (TDI, TDO, TCK, TMS).Akonáhle je proces dokončený, CPLD okamžite začne fungovať s programovanou logikou, bez toho, aby si vyžadoval napájací cyklus alebo externú konfiguračnú pamäť.

XC2C256-7TQ144C Výhody a nevýhody

Výhody

• Veľmi nízka pohotovostná energia, ideálna pre vzory napájané z batérie.

• Okamžitá prevádzka bez oneskorenia konfigurácie.

• Predvídateľné načasovanie pre ľahšie uzavretie dizajnu.

• Nahrádza viac diskrétnych logických čipov, šetrenie priestoru a náklady.

• Podporuje viac vstupno -výstupných napätí bez externých radičov úrovne.

Nevýhody

• Obmedzená logická kapacita v porovnaní s väčšími CPLDS alebo FPGA.

• Žiadne vstavané vysielače DSP, RAM alebo vysokorýchlostné vysielače.

• Zastarané, takže budúce získavanie budúcich získavaní.

• Nižší strop výkonu pre vysokorýchlostné aplikácie.

• Menšia flexibilita smerovania pre komplexné alebo nepravidelné návrhy.

XC2C256-7TQ144C Dimenzie obalu

|

Typ |

Parameter |

|

Typ balíka |

TQFP-144 |

|

Veľkosť tela balenie |

20 mm × 20 mm |

|

Rozstup |

0,5 mm |

|

Počet kolíkov |

144 |

|

Výška balíka (max) |

1,4 mm |

|

Hrúbka obalu (nominálna) |

1,0 mm |

|

Dĺžka olova |

0,45 mm ~ 0,75 mm |

|

Šírka olova |

0,17 mm ~ 0,27 mm |

|

Montáž |

Povrchová montáž |

|

Balík dodávateľských zariadení |

144-TQFP (20 × 20) |

XC2C256-7TQ144C Výrobca

XC2C256-7TQ144C sa vyrába Xilinx, vedúca spoločnosť v programovateľných logických riešeniach.Xilinx je široko uznávaný pre priekopnícke technológie FPGA a CPLD, ktoré poskytujú spoľahlivé a vysokovýkonné zariadenia pre priemyselné, komerčné a spotrebiteľské aplikácie.Dnes Xilinx pôsobí ako súčasť AMD, pokračovať v poskytovaní pokročilých programovateľných logických produktov so silnou dlhodobou podporou a inováciami.

Záver

XC2C256-7TQ144C sa vyznačuje nízkou spotrebou energie, rýchleho deterministického výkonu a flexibility I/O viacerých napätí, vďaka čomu je spoľahlivou voľbou pre moderné digitálne vzory.Jeho vyvážená kombinácia 256 makrocellov, 118 I/O pinov a pokročilej architektúry Interconnect podporuje širokú škálu funkcií riadenia, rozhrania a lepidla.S podporou programovania v systéme, funkciách úsporu výkonu DataGate a robustnými konfiguráciami I/O sa hladko integruje do zabudovaných systémov a prostredí zmiešaného napätia.

Datasheet pdf

XC2C256-7TQ144C DataShety:

O nás

ALLELCO LIMITED

Čítaj viac

Rýchly dopyt

Zašlite prosím dotaz, okamžite odpovieme.

často kladené otázky [FAQ]

1. Vyžaduje XC2C256-7TQ144C externú konfiguračnú pamäť?

Jednou z jeho výhod je okamžitá prevádzka.Konfigurácia je uložená interne, takže sa pripravuje na spustenie bez externej plesovej alebo flash pamäť.

2. Aké programovacie nástroje sú kompatibilné s XC2C256-7TQ144C?

Zariadenie môžete naprogramovať pomocou softvéru Xilinx Impact softvér pomocou programovacieho kábla JTAG.Mnohí tiež používajú kompatibilných programátorov JTAG tretích strán, ale uistite sa, že podporujú štandardy IEEE 1149.1/1532.

3. Môže XC2C256-7TQ144C nahradiť viac diskrétnych logických ICS vo vašom dizajne?

Áno.Vďaka svojim 256 makrocelkám a flexibilným vstupom do I/O môže tento CPLD integrovať niekoľko funkcií logiky a riadenia lepidla do jedného zariadenia, čo vám pomôže znížiť počet priestorov a počet komponentov.

4. Je XC2C256-7TQ144C vhodný pre aplikácie batérie s nízkym výkonom?

Áno.Vďaka svojej technológii Fast Zero Power (FZP) a veľmi nízkym pohotovostným prúdom je ideálny pre vždy na obvodoch, prenosných zariadeniach a vložených systémoch citlivých na energiu.

5. Môžete použiť XC2C256-7TQ144C na spracovanie vysokorýchlostného signálu?

Nie je navrhnutý pre vysokorýchlostné DSP alebo transceiverové úlohy.Aj keď poskytuje rýchle oneskorenia pin-to-kolíky, je najvhodnejšie pre riadenie, rozhranie a logiku načasovania, nie zložité spracovanie údajov.

EP2S60F672C4 FPGA: Funkcie, aplikácie, programovanie a príručka pre údaje

na 2025/10/4

EPM3256AFC256-7 Prehľad CPLD: Funkcie, pinout, programovanie a aplikácie

na 2025/10/3

Populárne príspevky

-

Komplexné súpravy inštrukcií: Ako zmenili výpočty?

na 8000/04/18 147778

-

USB-C Pinout a funkcie

na 2000/04/18 112036

-

Pomocou Xilinx Unified Simulation Primitive: Komplexný sprievodca dizajnom a simuláciou FPGA

na 1600/04/18 111352

-

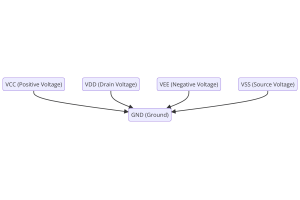

Napájacie napätia v elektronike: Význam VCC, VDD, VEE, VSS a GND

na 0400/04/18 83794

-

Sprievodca konektorom RJ45: Pinout, kábly, typy káblov a použitia

na 1970/01/1 79602

-

Konečný sprievodca k farebným kódom drôtu v moderných elektrických systémoch

Spôsob, akým naše elektrické systémy používajú farby, nie je len pre vzhľad.Každá farba drôtu teraz označuje špecifickú funkciu, čo uľahčuje správne identifikáciu a spracovanie elektrických kompone...na 1970/01/1 66978

-

Sprievodca čistením ventilu: funkcia, príznaky, testovanie a výmena za optimálny výkon motora

Čistý ventil je kľúčovou súčasťou systému automobilu, ktorý pomáha udržiavať vzduch čistý riadením výparov paliva skôr, ako môžu uniknúť do atmosféry.To nielen pomáha životnému prostrediu znížením ...na 1970/01/1 63111

-

Kvalita (Q) Faktor: Rovnice a aplikácie

Faktor kvality alebo „Q“ je dôležitý pri kontrole, ako dobre induktory a rezonátory pracujú v elektronických systémoch, ktoré používajú rádiové frekvencie (RF).'Q' meria, ako dobre obvod minimalizu...na 1970/01/1 63044

-

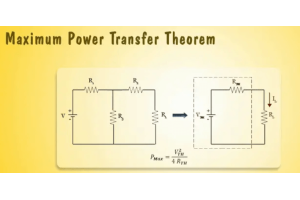

Dosiahnutie maximálneho výkonu s maximálnou vetou prenosu energie

Maximálna veta prenosu energie vysvetľuje, ako energia zo zdroja, napríklad batéria alebo generátor, tečie na pripojené zaťaženie.Zobrazuje presnú podmienku, keď zaťaženie prijíma najviac energie.T...na 1970/01/1 54097

-

Špecifikácie batérie A23 a kompatibilita

Batéria A23 je malá batéria v tvare valca s vysokým napätím.Nazýva sa tiež 23A, 23ae alebo MN21, beží na 12 voltoch a oveľa vyšších ako batérie AA alebo AAA.Vďaka jeho špeciálnemu dizajnu ...na 1970/01/1 52198