EP2S60F672C4 FPGA: Funkcie, aplikácie, programovanie a príručka pre údaje

V tejto príručke získate jasný prehľad EP2S60F672C4, výkonného FPGA z rodiny Stratix II spoločnosti Intel.Dozviete sa o jej hlavných funkciách, architektúre, štruktúre blokov a technických špecifikáciách, aby ste pochopili, ako sa zmestí do pokročilých digitálnych návrhov.Tiež vás prevedie svojimi programovacími krokmi, aplikáciami, výhodami a nevýhodami, aby ste presne videli, kde a ako je možné toto zariadenie použiť.Katalóg

Čo je EP2S60F672C4?

Ten EP2S60F672C4 je FPGA s vysokou hustotou od spoločnosti Intel (predtým Altera), ktorá patrí do rodiny Stratix II.Postavená na procese medi SRAM s rozmermi 90 nm, 1,2 V, poskytuje značnú logickú kapacitu v rámci balíka FBGA 672-Ball, vďaka čomu je ideálny pre zložité digitálne systémy.V rámci série EP2S je zariadenie „60“ v strednom rozsahu zostavy Stratix II, ktoré ponúka silnú rovnováhu logickej hustoty, vloženej pamäte a I/O zdrojov.Tento FPGA, známy svojou robustnou architektúrou a spoľahlivosťou, zostáva dôveryhodnou voľbou v mnohých pokročilých dizajnoch.

Hľadáte EP2S60F672C4?Kontaktujte nás a skontrolujte aktuálne zásoby, dodací čas a ceny.

EP2S60F672C4 CAD modely

Symbol EP2S60F672C4

EP2S60F672C4 Footprint

EP2S60F672C4 3D model

Funkcie EP2S60F672C4

• Advanced 90 nm, 1,2 V CMOS proces

EP2S60F672C4 sa vyrába na procese CMOS CMOS s rozmermi 90 nm, ktorý beží pri jadrovom napätí 1,2 V.Táto technológia umožňuje vysokú rýchlosť, zníženú spotrebu energie a väčšiu hustotu logiky v porovnaní so staršími generáciami FPGA.

• Adaptívny logický modul (ALM) architektúra

Zariadenie používa almužny ako svoj logický stavebný blok namiesto tradičných logických prvkov.Táto architektúra zlepšuje využitie zdrojov, čo umožňuje efektívne implementáciu zložitejších logických funkcií v rámci tej istej oblasti kremíka.

• Vysoká hustota logiky

FPGA s približne 60 440 logickými prvkami (24 176 almužny) podporuje veľké a sofistikované digitálne návrhy.Vďaka tejto vysokej kapacite je vhodná pre aplikácie, ako je spracovanie signálu, komunikácia a zabudované riadiace systémy.

• Pamäť Trimatrix ™ na čipe

EP2S60F672C4 integruje tri typy blokov RAM (M512, M4K a M-RAM), aby poskytli celkovo približne 2,4 mbity vloženej pamäte.Táto zmes umožňuje efektívne implementovať malé FIFO, stredné vyrovnávacie pamäte a veľké dvojpontážne spomienky.

• Vyhradené bloky DSP

Zariadenie obsahuje 36 vyhradených blokov DSP určených pre aritmetické operácie, ako sú multiplikácie, akumulácie a filtrovanie FIR.Tieto bloky zvyšujú výkonnosť pri výpočtových úlohách a zároveň ukladajú všeobecné logické zdroje.

• Vysokorýchlostná integrita I/O a signálu

Podporuje rôzne jednosmerné a diferenciálne I/O štandardy spolu s obvodmi dynamického zarovnania fázy (DPA).Tieto vlastnosti umožňujú stabilný a vysokorýchlostný prenos údajov až do 1 Gbps, čo zabezpečuje spoľahlivú komunikáciu s externými komponentmi.

• Podpora rozhrania externej externej pamäte

FPGA je kompatibilný s DDR, DDR2, QDR II, RLDRAM II a ďalšími pamäťovými normami.Vstavaná podpora rozhrania zjednodušuje návrh dosky a dosahuje vysokú priepustnosť údajov pre aplikácie náročné na pamäť.

• Flexibilná správa hodín

Až 12 na čipových PLL umožňuje násobenie hodín, delenie, posun fázy a prepínanie bez závad.Môžete doladiť domény hodín a znížiť Jitter, čo podporuje vnútorné frekvencie hodín až do 500-550 MHz.

• Šifrovanie a rekonfigurácia bitov

EP2S60F672C4 podporuje šifrovanie Bitstream založeného na AES na zabezpečenie duševného vlastníctva.Ponúka tiež schopnosť vzdialenej rekonfigurácie, ktorá umožňuje aktualizácie v teréne bez výmeny zariadenia.

Bloková schéma Stratix II

Blokový diagram Stratix II, ako je znázornené pre EP2S60F672C4, ilustruje interné usporiadanie logiky, pamäte a DSP zdrojov, ktoré tvoria jadro FPGA.Bloky logického poľa (laboratóriá) sú usporiadané do pravidelnej mriežky, obklopenej vloženými stĺpcami RAM a DSP, ktoré poskytujú rýchle aritmetické a čipové schopnosti úložiska.Periférne vstupno -výstupné prvky a hodiny siete rámujú túto štruktúru, čo umožňuje efektívny prenos údajov a riadenie časovania medzi zariadeniami FPGA a externými zariadeniami.Tento diagram je dôležitý, pretože pomáha pochopiť, ako sú rôzne funkčné bloky fyzicky usporiadané, čo im umožňuje optimalizovať umiestnenie, smerovanie a celkový výkon systému.

Stratix II I/O Banks Diagram

Tento diagram Stratix II I/O Banks ilustruje, ako sú zoskupené vstupné/výstupné kolíky EP2S60F672C4 a aké elektrické štandardy každá skupina podporuje.Každá banka I/O je navrhnutá tak, aby zvládla špecifické úrovne napätia, typy signalizácie a funkcie, ako sú štandardy LVTTL, SSTL, LVD alebo vstupných štandardov.Usporiadanie ukazuje, ako sú rôzne banky (napr. 1, 2, 5, 6 vs. 3, 4, 7, 8 atď.) Optimalizované pre všeobecné I/O alebo vysokorýchlostné diferenciálne signalizácie, vrátane podpory pre vstupy hodín LVD/LVPECL na okrajoch.Pochopenie tejto štruktúry je dôležité pri priraďovaní kolíkov, pretože správny výber banky zaisťuje elektrickú kompatibilitu, zjednodušuje smerovanie dosiek a maximalizuje výkon FPGA vo vysokorýchlostných dizajnoch.

Špecifikácie EP2S60F672C4

|

Typ |

Parameter |

|

Výrobca |

Alterna/Intel |

|

Séria |

Stratix® II |

|

Balenie |

Podnos |

|

Stav |

Zastaraný |

|

Počet laboratórií/CLB |

3022 |

|

Počet logických prvkov/buniek |

60 440 |

|

Celkový baranový kúsok |

2 544,192 |

|

Počet I/O |

492 |

|

Napätie - napájanie |

1,15 V ~ 1,25 V |

|

Montáž |

Povrchová montáž |

|

Prevádzková teplota |

0 ° C ~ 85 ° C (TJ) |

|

Balenie |

672-bbga |

|

Balík dodávateľských zariadení |

672-FBGA (27 × 27) |

|

Základné číslo produktu |

EP2S60 |

Aplikácie EP2S60F672C4

1. Spracovanie digitálneho signálu (DSP) a filtrovanie

EP2S60F672C4 je vhodný na implementáciu vysokovýkonných funkcií DSP, ako sú FIR a IIR filtre, spracovanie FFT a zložité aritmetické operácie.Jeho vyhradené bloky DSP sa efektívne zaoberajú násobkami a akumuláciami, ktoré uvoľňujú všeobecné logické zdroje pre ďalšie úlohy.Pamäť On-Chip Trimatrix ™ umožňuje hladké vyrovnávanie údajov a potrubie, ktoré je vynikajúce pre spracovanie v reálnom čase pri vysokých vzorkovacích frekvenciách.Vďaka tomu je zariadenie ideálne pre pokročilé aplikácie zvuku, videa a radarového signálu.

2. Vysokorýchlostná komunikácia a vytváranie sietí

Vysokorýchlostné I/O rozhrania FPGA a obvody Dynamic Phase Loverment (DPA) podporujú spoľahlivý prenos údajov na úrovni gigabitu.Môže implementovať komunikačné protokoly a funkcie fyzickej vrstvy pre systémy, ako sú smerovače, prepínačy a prepojenia bezprostredných.Vďaka svojej veľkej logickej kapacite a flexibilných PLL dokáže spravovať komplexné konverzie načasovania a protokolu medzi viacerými vysokorýchlostnými rozhraniami.Tieto schopnosti sú silne vhodné pre telekomunikačnú infraštruktúru a sieťové sieťové vybavenie s vysokou šírkou.

3. Ovládače pamäte a systémy spracovania údajov

EP2S60F672C4 podporuje rôzne rozhrania externej pamäte vrátane DDR, DDR2, RLDRAM II a QDR II, vďaka čomu je ideálny na navrhovanie ovládačov pamäte s vysokou šírkou šírky.Dokáže zvládnuť vyrovnávanie údajov, generovanie adries a arbitráž s vysokou rýchlosťou s minimálnou latenciou.Kombinácia sietí rýchlych hodín a zabudovaných blokov RAM umožňuje efektívne riadenie veľkých dátových tokov.Vďaka tomu je FPGA vhodná na spracovanie obrazu, streamovanie videa a vedecké výpočtové platformy, ktoré sa spoliehajú na vysokú priepustnosť údajov.

4. Vlastná logika a zabudované zrýchlenie

S viac ako 60 000 logickými prvkami a bohatými správami hodín môže FPGA hostiť prispôsobené hardvérové urýchľovače pre konkrétne algoritmy.Dizajnéri ho často používajú na vykladanie výpočtovo náročných úloh z CPU, ako je šifrovanie, analýza protokolu alebo kontrolné slučky v reálnom čase.Môže tiež integrovať viac funkčných blokov, vďaka čomu je vhodný pre zložité vzory podobné SOC.Vďaka tejto flexibilite je cenná v aplikáciách, ako je priemyselná automatizácia, bezpečnostné systémy a riadiace jednotky letectva.

5. Prototypovanie a platformy rozvoja vzdelávania

Zariadenie EP2S60 sa bežne vyskytuje vo vývojových súpravách FPGA používaných na prototypovanie, testovanie a akademický výskum.Jeho rovnováha logickej kapacity, počtu I/O a schopností DSP umožňuje inžinierom a študentom implementovať a overiť úplné systémy na jednom čipe.Podporuje rýchlu iteráciu digitálnych návrhov, čo umožňuje overenie hardvéru pred zaviazaním sa k rozvoju ASIC.Mnoho univerzít a laboratórií výskumu a vývoja ho používa na výučbu pokročilého digitálneho dizajnu a konceptov spracovania signálov.

EP2S60F672C4 Podobné časti

|

Špecifikácia |

EP2S60F672C4 |

EP2S60F672C3N |

EP2S60F672C5 |

EP2S60F672C5N |

EP2S60F672I4

|

EP2S60F672I3N |

|

Rodina / séria |

Stratix II |

Stratix II |

Stratix II |

Stratix II |

Stratix II |

Stratix II |

|

Logické prvky (LE) |

60 440 |

60 440 |

60 440 |

60 440 |

60 440 |

60 440 |

|

Almužna |

24,176 |

24,176 |

24,176 |

24,176 |

24,176 |

24,176 |

|

Balík |

FBGA-672 |

FBGA-672 |

FBGA-672 |

FBGA-672 |

FBGA-672 |

FBGA-672 |

|

Rýchlosť |

C4 (STD) |

C3 (rýchlejšie) |

C5 (rýchlejšie) |

C5 (rýchlejšie) |

I4 (std) |

I3 (rýchlejšie) |

|

Teplota |

Komerčné (0 ~ 70 ° C) |

Obchodný |

Obchodný |

Obchodný |

Priemyselné (-40 ~ 100 ° C) |

Priemyselné (-40 ~ 100 ° C) |

|

PIN/O |

492 |

492 |

492 |

492 |

492 |

492 |

|

Pamäť |

2,4 Mbit |

2,4 Mbit |

2,4 Mbit |

2,4 Mbit |

2,4 Mbit |

2,4 Mbit |

|

Napätie jadra |

1,2 V |

1,2 V |

1,2 V |

1,2 V |

1,2 V |

1,2 V |

|

Kľúčový rozdiel |

Základná komerčná rýchlosť |

C3 Speed Bin, „N“ bez olova |

Bin |

Variant s vyššou rýchlosťou, variant „N“ |

Priemyselná teplota, rovnaká hustota |

Priemyselná, rýchlejšia rýchlosť, bez olova |

EP2S60F672C4 Programovacie kroky

Predtým, ako budete môcť vo svojom dizajne použiť FPGA EP2S60F672C4 FPGA, musíte ho správne nakonfigurovať pomocou zostaveného bitov.Tento proces zahŕňa prípravu programovacieho súboru, nastavenie hardvérového rozhrania a zabezpečenie správneho načítania konfigurácie pri zapnutí.

Krok 1: Vytvorte a zostavte svoj dizajn

Začnete vývojom logického dizajnu pomocou softvéru Intel Quartus II.Po dokončení návrhu ho zostavujete na vygenerovanie programovacieho súboru (.SOF alebo .POF) špecificky pre zariadenie EP2S60F672C4.Proces kompilácie kontroluje načasovanie, priradenia PIN a využitie zdrojov, aby sa zabezpečilo, že váš dizajn zapadá do architektúry FPGA.Po zostavení je váš BitStream pripravený na konfiguráciu zariadenia.

Krok 2: Nastavte programovací hardvér

Ďalej pripravujete rozhranie fyzického programovania medzi počítačom a doskou FPGA.Zvyčajne to zahŕňa pripojenie USB-Blaster alebo kompatibilného kábla JTAG k portu JTAG zariadenia.Mali by ste overiť, či Quartus II rozpoznáva programátor a že cieľové zariadenie je správne zistené.Tento krok zaisťuje stabilnú komunikáciu pred začatím konfiguračného procesu.

Krok 3: Načítať programovací súbor do zariadenia

Pomocou nástroja programátora Quartus II pridáte kompilovaný súbor .SOF alebo .POF a vyberiete EP2S60F672C4 zo zoznamu zistených zariadení.Potom iniciujte programovaciu sekvenciu, počas ktorej sa Bitstream prenáša a načíta do konfiguračných buniek SRAM FPGA.Mali by ste monitorovať riadky a stavové správy o pokroku, aby ste potvrdili úspešnú konfiguráciu.Po dokončení FPGA začne okamžite vykonávať programovanú logiku.

Krok 4: Overte konfiguráciu a prevádzku

Po programovaní overíte, či zariadenie funguje podľa plánu.Quartus II poskytuje možnosť overenia na kontrolu konfiguračných signálov CRC a stavu, čím sa zabezpečí správne načítanie dizajnu.Môžete tiež otestovať svoje I/O funkcie alebo spustiť funkčnú simuláciu, aby ste potvrdili správanie systému.Tento posledný krok zaisťuje, že váš dizajn je na hardvéri plne funkčný a stabilný.

EP2S60F672C4 Výhody a nevýhody

Výhody

• Vysoká hustota logiky pre zložité vzory

• Dobrý pomer výkonu k nákladom

• Ľahká migrácia v rámci tej istej rodiny

• Stabilné a zrelé vývojové nástroje

• Osvedčená spoľahlivosť v priemyselnom používaní

Nevýhody

• Zastarané a ťažšie sa získavajú

• Vyššia spotreba energie ako novšie FPGA

• Žiadne moderné vysokorýchlostné vysielače

• Zložitejšie zatvorenie načasovania pri vysokom využití

• Obmedzená škálovateľnosť pre budúce protokoly

EP2S60F672C4 rozmery obalu

|

Typ |

Parameter |

|

Typ balíka |

672-FBGA (Fineline BGA) |

|

Veľkosť tela (L × W) |

27,00 mm × 27,00 mm |

|

Celková výška balíka (a) |

Max 3,50 mm |

|

Výška odstupu (A1) |

Min 0,30 mm |

|

Hrúbka substrátu (A2) |

Max. 3,00 mm |

|

Priemer lopty (B) |

0,50 mm - 0,70 mm |

|

Pitch Lall (E) |

1,00 mm |

|

Počet loptičiek |

672 |

|

Montáž |

Povrchová montáž |

|

Popis |

FBGA, mriežka 27 × 27 mm |

Výrobca EP2S60F672C4

FPGA EP2S60F672C4 sa vyrába Spoločnosť Altera Corporation, popredný priekopník v programovateľných logických zariadeniach.V roku 2015 získala Altera Zamerať, a produkt teraz spadá pod programovateľné riešenia spoločnosti Intel (PSG), ktorá naďalej podporuje a dodáva rodiny FPGA spoločnosti Altera.Spoločnosť Intel udržiava líniu Stratix II ako súčasť svojho staršieho portfólia produktov, zabezpečuje dokumentáciu, podporu nástrojov a dlhodobú dostupnosť pre priemyselné a komunikačné aplikácie.

Záver

EP2S60F672C4 kombinuje vysokú logickú hustotu, flexibilnú pamäťovú architektúru a robustné funkcie I/O na podporu zložitých digitálnych systémov.Jeho návrh založený na ALM, pamäť Trimatrix ™, bloky DSP a funkcie správy hodín umožňujú efektívnu implementáciu náročných aplikácií.Aj keď ponúka osvedčenú podporu spoľahlivosti a zrelej podpory rozvoja, čelí obmedzeniam, ako je zastaranosť a nedostatok moderných vysielateľov v porovnaní s novšími generáciami FPGA.Celkovo je jeho vyvážený výkon a všestrannosť solídnou voľbou pre spracovanie signálu, komunikáciu, manipuláciu s údajmi a prototypovanie aplikácií.

Datasheet pdf

EP2S60F672C4 DataShety:

O nás

ALLELCO LIMITED

Čítaj viac

Rýchly dopyt

Zašlite prosím dotaz, okamžite odpovieme.

často kladené otázky [FAQ]

1. Môže EP2S60F672C4 pracovať s modernými rozhraniami pamäte DDR?

Áno, podporuje rozhrania DDR, DDR2, QDR II a RLDRAM II, ktoré pokrývajú mnoho bežných štandardov externej pamäte.Vďaka tomu je vhodný pre aplikácie na spracovanie údajov s vysokou šírkou.

2. Vyžaduje EP2S60F672C4 špeciálne zaobchádzanie alebo úložisko?

Áno, rovnako ako iné komponenty zabalené BGA, by sa mal skladovať v balení kontrolovanom vlhkosti a mal by sa manipulovať s ochranou ESD.Podľa správnych postupov skladovania pomáha udržiavať počas montáže spájanie a spoľahlivosť zariadení.

3. Ako môžete znížiť spotrebu energie v dizajnoch EP2S60F672C4?

Môžete optimalizovať využitie logiky, nepoužité hodiny brány, nižšie vstupno-výstupné napätia, ak je to možné, a využiť možnosti syntézy sily v Quartus II, aby ste minimalizovali celkové vyzdvihnutie energie.

4. Aké programovacie nástroje sú potrebné pre EP2S60F672C4?

Na konfiguráciu zariadenia budete potrebovať softvér Intel Quartus II na návrh, kompiláciu a programovanie spolu s USB-blasterom alebo kompatibilným káblom JTAG.

5. Podporuje EP2S60F672C4 aktualizácie v teréne alebo vzdialenú rekonfiguráciu?

Áno, podporuje AES založené šifrovanie bitov a vzdialenú rekonfiguráciu, čo vám umožňuje bezpečne aktualizovať váš systém bez fyzickej výmeny FPGA.

Všetko o lfxp6c-3fn256c mriežky polovodiča

na 2025/10/6

XC2C256-7TQ144C CPLD: PINOUT, Funkcie, programovanie a sprievodca údajmi

na 2025/10/3

Populárne príspevky

-

Komplexné súpravy inštrukcií: Ako zmenili výpočty?

na 8000/04/19 147782

-

USB-C Pinout a funkcie

na 2000/04/19 112062

-

Pomocou Xilinx Unified Simulation Primitive: Komplexný sprievodca dizajnom a simuláciou FPGA

na 1600/04/19 111352

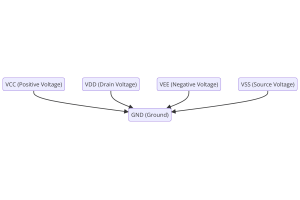

-

Napájacie napätia v elektronike: Význam VCC, VDD, VEE, VSS a GND

na 0400/04/19 83819

-

Sprievodca konektorom RJ45: Pinout, kábly, typy káblov a použitia

na 1970/01/1 79639

-

Konečný sprievodca k farebným kódom drôtu v moderných elektrických systémoch

Spôsob, akým naše elektrické systémy používajú farby, nie je len pre vzhľad.Každá farba drôtu teraz označuje špecifickú funkciu, čo uľahčuje správne identifikáciu a spracovanie elektrických kompone...na 1970/01/1 66999

-

Sprievodca čistením ventilu: funkcia, príznaky, testovanie a výmena za optimálny výkon motora

Čistý ventil je kľúčovou súčasťou systému automobilu, ktorý pomáha udržiavať vzduch čistý riadením výparov paliva skôr, ako môžu uniknúť do atmosféry.To nielen pomáha životnému prostrediu znížením ...na 1970/01/1 63124

-

Kvalita (Q) Faktor: Rovnice a aplikácie

Faktor kvality alebo „Q“ je dôležitý pri kontrole, ako dobre induktory a rezonátory pracujú v elektronických systémoch, ktoré používajú rádiové frekvencie (RF).'Q' meria, ako dobre obvod minimalizu...na 1970/01/1 63062

-

Dosiahnutie maximálneho výkonu s maximálnou vetou prenosu energie

Maximálna veta prenosu energie vysvetľuje, ako energia zo zdroja, napríklad batéria alebo generátor, tečie na pripojené zaťaženie.Zobrazuje presnú podmienku, keď zaťaženie prijíma najviac energie.T...na 1970/01/1 54097

-

Špecifikácie batérie A23 a kompatibilita

Batéria A23 je malá batéria v tvare valca s vysokým napätím.Nazýva sa tiež 23A, 23ae alebo MN21, beží na 12 voltoch a oveľa vyšších ako batérie AA alebo AAA.Vďaka jeho špeciálnemu dizajnu ...na 1970/01/1 52215