Pochopenie sily západky S-R: brána k modernej elektronike

Západy sú jednoduché digitálne zariadenia, ktoré ukladajú jeden kúsok informácií a uchovávajú túto hodnotu, až kým nezíska nové vstupné signály.Používajú sa v digitálnych systémoch na dočasné uchovávanie binárnych údajov.Západky je možné vyrobiť pomocou rôznych druhov základných logických brán, ako je a, alebo nie, NAND a ani brány.Tento článok skúma návrh, funkcie, variácie a použitie západky S-R, zdôrazňuje svoju najlepšiu úlohu v modernej elektronike a jeho použitie v praktických obvodoch a digitálnych logických simuláciách.

Katalóg

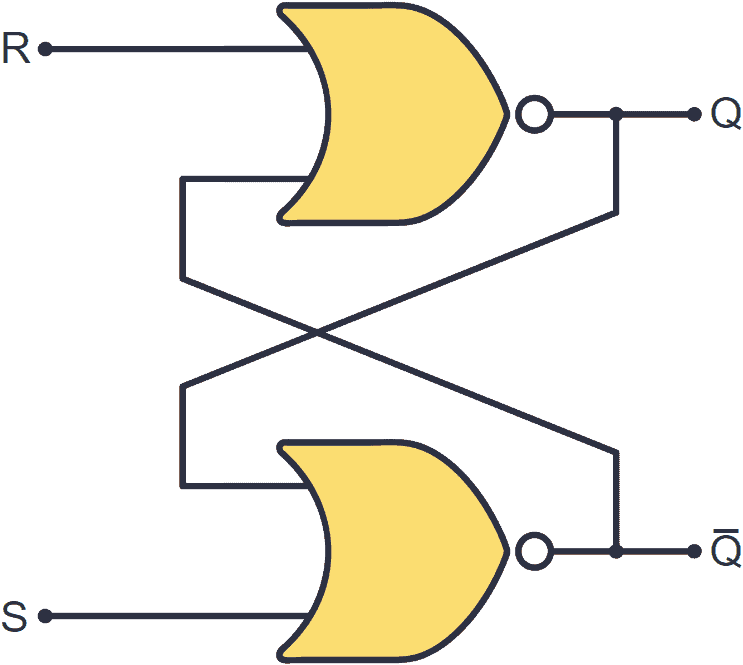

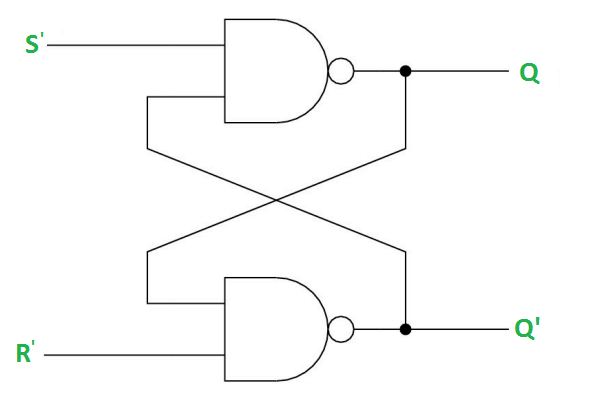

Obrázok 1: Schéma obvodu západky S-R

Štruktúra západky S-R

Západná kameň S-R (Set-Reset), základný kameň v digitálnej elektronike, je bistabilný multivibrátor.Je schopný udržať jeden z dvoch odlišných stabilných stavov neurčito bez vonkajšieho vstupu.Táto funkcia robí SR Latch hlavným komponentom v oblasti ukladania a prepínania pamäte na rôznych elektronických zariadeniach.

Štrukturálne sa západka SR pozostáva z dvoch vzájomne prepojených ani brány usporiadaných v návrhu spätnej slučky.Na tomto konkrétnom usporiadaní záleží, pretože ponúka predpoklady pre bistabilitu.Výstup každá z nich je pripojený priamo k vstupu druhého, čím vytvára kontinuálnu slučku spätnej väzby, ktorá podporuje činnosť západky.

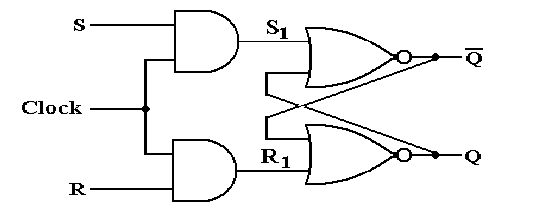

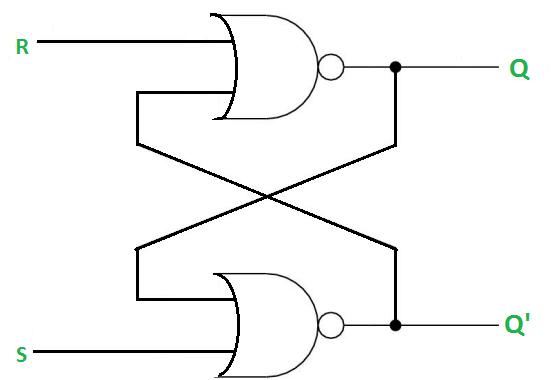

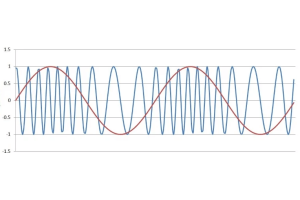

Obrázok 2: Západka S-R a Signál hodín (CLK)

Bránu SR Latch sa rozširuje na základný dizajn a zavádza ďalší, vstup: hodinový signál (CLK).Toto vylepšenie obsahuje vstup hodín, ktorý prináša vrstvu riadenia a integruje operácie západky do systémov, ktoré vyžadujú synchronizáciu.Táto synchronizácia sa zaviazala, pretože určuje presné momenty, keď sa západka môže zmeniť stavy, výstižne opísané pojmom „hradený“.Zahrnutie hodinového signálu zaisťuje, že zmeny vo výstupnom stave západky sa vyskytnú iba počas aktívnej fázy hodín, zvyčajne na stúpajúcom alebo padajúcom okraji signálu CLK.

Zavedenie vstupu CLK nielen zachováva vlastnosti základnej západky SR, ale tiež spája svoju činnosť s dočasnou dynamikou väčších digitálnych systémov.Táto túžba porovnania po udržaní integrity údajov a zabezpečenie toho, aby sa prechody stavu vyskytli bez závady alebo nezamýšľaných zmien, najmä v zložitých konfiguráciách obvodov, kde môžu interagovať viac západiek.Ovládaním, keď západka reaguje na príkazy set a reset, môže systém vyhnúť problémom, ako sú rasové podmienky a iné chyby súvisiace s načasovaním, ktoré by inak mohli narušiť stabilitu a výkon systému.

Operačné štáty západky S-R

Jeho prevádzka závisí od vstupov dvoch ovládacích signálov: set (s) a reset (R).Tu vysvetlíme, ako tieto vstupy ovplyvňujú výstupy a stavy západky SR.

Prípad 1: Stavte stav

Ak je vstup (s) vysoký (1) a reset (R) vstup je nízky (0), západka zadá nastavenú podmienku.V tomto stave bude brána NAND pripojená k vstupu R vyvodiť nízky signál z dôvodu vysokého vstupu z S. Tento nízky signál spôsobí, že druhá brána NAND na výstupe vysoký signál, nastavuje Q na vysoký (1) a q-barna nízku (0).Tento stav je stabilný a udrží Q vysoký, kým sa vstupy nezmenia, čo ukazuje schopnosť západky ukladať vysoký stav.

Obrázok 3: Stavový stav

Prípad 2: Stav resetovania

Ak je S nízka (0) a R sú vysoké (1), západka zadá stav reset.Vysoký vstup na R a nízky vstup na S spôsobujú, že brána NAND je pripojená k výstupu nízkemu signálu.Tento nízky signál nastaví Q na nízku (0) a q-bar na vysokú (1), čo účinne resetuje západku.To demonštruje schopnosť západky vrátiť sa do stabilného nízkeho stavu v Q, keď je vzhľadom na správne vstupy.

Obrázok 4: Stav resetovania

Prípad 3: Neplatný stav

Ak sú S a R nízke (0), oba vstupy do brán NAND sú nízke, čo spôsobuje, že obidva výstupy Q a Q-BAR sa zvýšia.Tento stav sa nazýva neplatný alebo zakázaný, pretože porušuje základné pravidlo, že q a q-bar by mali byť vždy protiklady.Tento scenár zdôrazňuje obmedzenie západky SR, zdôrazňuje dôležitosť vyhýbania sa týmto nestabilným stavom prostredníctvom správneho riadenia vstupov.

Obrázok 5: Neplatný stav

Prípad 4: Podmienka

Ak sú oba vstupy vysoké (1), výstupy závisia skôr od predchádzajúceho stavu západky ako od aktuálnych vstupov.Toto je známe ako podmienka držania, kde Q a Q-BAR zostávajú nezmenené a zachovávajú posledný platný stav západky.Pre niektoré aplikácie je dôležité, aby ste boli schopní udržiavať latkovaný stav po dlhú dobu bez modifikácie, ako sú bunky ukladania pamäte, kde je integrita údajov veľmi dôležitá.

Obrázok 6: Stav Hold

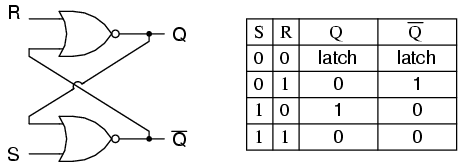

Západka S-R so stolom pravdy

Táto tabuľka nie je len teoretický nástroj, ale je tiež praktický pre dizajnérov obvodov aj študentov.Pomáha im vidieť, ako sa západka správa za mnohých podmienok.Nižšie uvádzame komplexnú tabuľku pravdy pre SR Latch, po ktorej nasledujú vysvetlenia a praktické poznatky pre každú podmienku.

|

Siež |

R |

Otázka |

Q-bar |

Uviesť |

|

0 |

0 |

1 |

1 |

Neplatný |

|

0 |

1 |

0 |

1 |

Vynulovanie |

|

1 |

0 |

1 |

0 |

Súbor |

|

1 |

1 |

Otázka |

Q-bar |

Zadržať |

Graf 1: SR

Stopa pravdy

Vysvetlenie každého riadku

Nastavte podmienku (s = 1, r = 0): Tento riadok ukazuje, že keď je S vysoký a r je nízky, Q je nastavený na vysoké (1) a q-bar na nízku (0).Toto odráža reakciu obvodu na príkaz set, ktorý účinne ukladá „1“.

Reset Stav (s = 0, r = 1): Tu vstupy označujú resetovaciu operáciu.V dôsledku toho sa Q resetuje na nízku (0) a Q-Bar je nastavený na vysokú (1).Tento stav demonštruje schopnosť západky vrátiť sa k „0“.

Neplatná podmienka (S = 0, r = 0): Oba výstupy sa v tomto stave zvyšujú, čomu sa všeobecne vyhýba, pretože vedie k tomu, že oba výstupy sú identické.To môže viesť k nestabilite alebo nedefinovanému správaniu v západke, pretože porušuje pravidlo, že Q a Q-Bar by mali byť vždy protiklady.

Podmienka (S = 1, R = 1): V tomto scenári si západka udržuje svoj predchádzajúci stav a predstavuje svoju schopnosť držať posledný stavový stav, pokiaľ nie je výslovne neprikázané zmeniť sa.

Praktické poznatky a tipy

Pochopenie výstupov: Vždy nezabudnite, že Q a Q-BAR sú ideálne doplnky.Akákoľvek odchýlka od tohto pravidla (ako je vidieť v neplatnom stave) naznačuje problém alebo nesprávnu konfiguráciu.

Vyhýbanie sa neplatným štátom: Je nevyhnutné, aby dizajnéri boli opatrní, aby zabránili situácii, keď sú S a R nízke.Implementácia dodatočnej logiky alebo blokovania môže pomôcť zabrániť tomuto stavu.

Využitie podmienky držania: Podmienka držania môže byť obzvlášť vhodná v aplikáciách, ktoré si vyžadujú uchovávanie údajov v priebehu času.Udržiavanie integrity údajov môže závisieť od zabezpečenia toho, aby západka neúmyselne prešla do stavu nastavenia alebo resetovania.

Interpretácia tabuľky pravdy: Pri navrhovaní alebo ladiacich obvodoch odkazujte na tabuľku pravdy, aby ste predpovedali, ako zmeny vo vstupe ovplyvnia výstup, najmä v zložitých obvodoch, kde sa používa viac západiek.

Funkčná dynamika západky S-R

Západka S-R (Set-Reset) funguje dobre, iba ak sú jej vstupy správne spravované.Aby ste pochopili, ako funguje, musíte vedieť, ako rôzne vstupné kombinácie ovplyvňujú výstupy, q a q-bar (opak q).

Obrázok 7: Západka S-R

Ak sú obidve nastavené a reset (R) aktivované súčasne (s = 1 a r = 1), západka prechádza do „zakázaného stavu“, kde sú oba výstupy, q a q-bar, 0.Toto je problém, pretože normálne by mali byť q a q-bar protiklady.

Za normálnych podmienok na nastavenie západky aktivujete S (nastavte S na 1) a deaktivujte r (nastavte R na 0).Vďaka tomu je Q go (1) a Q-Bar Go Low (0), zobrazuje západku a môže uložiť 1. Na resetovanie západky, aktivujete R (nastavte R na 1) a deaktivujte S (nastavte S na 0).Vďaka tomu je Q Go Low (0) a Q-Bar vysoký (1), čo ukazuje, že západka sa môže vyčistiť a uložiť 0.

Ak sú oba vstupy deaktivované (s = 0 a r = 0), západka zachováva svoj posledný stav, buď nastavený alebo resetovaný.To je dobré na ukladanie údajov alebo udržiavanie stavu bez potreby nepretržitého vstupu.

Rasové podmienky môžu skomplikovať prevádzku S-R LATCH.Tieto chyby sa vyskytujú, keď sa výstupy do značnej miery spoliehajú na načasovanie vstupných zmien, čo vedie k nepredvídateľným výsledkom, ak sa vstupy menia takmer v rovnakom čase.Aby sa tomu zabránilo a zabezpečilo sa, že západka funguje spoľahlivo, často sa používajú mechanizmy oneskorenia.Tieto oneskorenia zabezpečujú, aby sa jeden vstup aktivoval potom, čo druhý má čas na stabilizáciu.Aby sa západka použila v digitálnych obvodoch, kde sa vyžaduje presné načasovanie, musí vykonávať dôsledne a udržiavať stabilné výstupy.To je možné pomocou kontrolovaného načasovania.

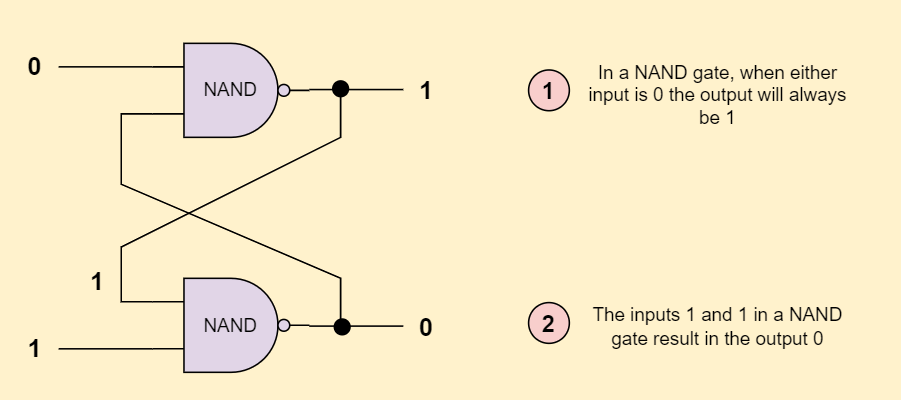

Logický diagram západky S-R

SR západka je základný sekvenčný logický obvod s dvoma hlavnými konfiguráciami: NOR alebo NAND GATES.Každé nastavenie ovplyvňuje spôsob, akým západka funguje, a reaguje na vstupy, čo umožňuje prispôsobenie rôznych elektronických aplikácií.

Obrázok 8: Logický diagram predstavuje západku S-R pomocou brány NAND

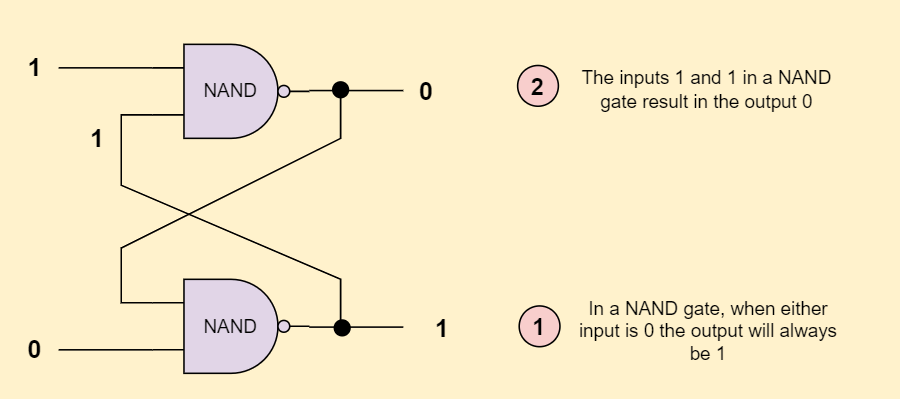

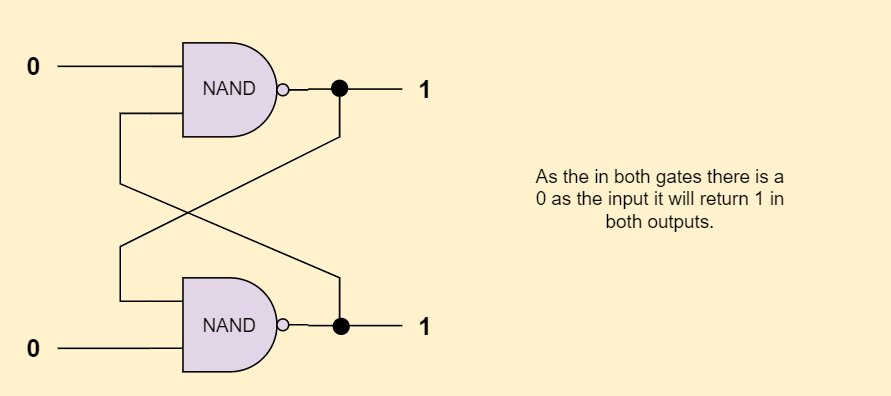

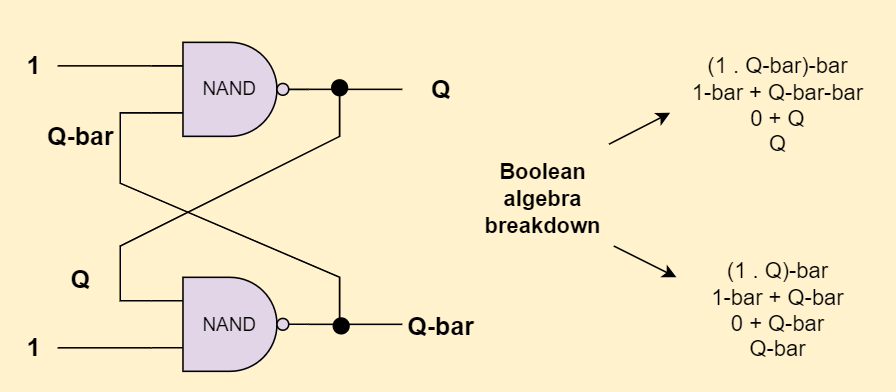

Implementácia pomocou brán NAND

Pri stavbe západky SR s Nand Gates sa na udržanie svojho stavu používa spätná väzba.Toto nastavenie umožňuje západke udržiavať svoj predchádzajúci stav, keď sú nízke vstupy (S a R).Nand brány výstup vysoký, pokiaľ nie sú vysoké oba vstupy.Stav západky sa zmení, keď je jeden vstup vysoký a druhý je nízky.Najlepšie je vyhnúť sa nastaveniu S a R vysoko súčasne, pretože to núti obidva výstupy, aby sa znížil, čo vedie k nedefinovanému stavu, v ktorom výstupy už nie sú doplňujúce.Správne riadenie vstupov je nevyhnutnosťou zabrániť nestabilite v NANS-založených na SR západky.

Implementácia pomocou NOR GATES

Použitie NOR BATES pre SR západku zmení prevádzkové podmienky v porovnaní s bránami NAND.V tejto konfigurácii drží západka svoj stav, keď sú oba vstupy vysoké.Zmeny západky sa zmení, keď je jeden vstup nízky a druhý je vysoký.Ani brány výstupné vysoké iba vtedy, ak sú oba vstupy nízke.Toto nastavenie je užitočné v obvodoch, v ktorých je predvolený stav, aby mal oba výstupy nízky, čo zabezpečuje predvídateľný výstup za podmienok vysokej vstupov.Najlepšie je však vyhnúť sa nastaveniu obidvoch vstupov na nízku úroveň súčasne, pretože to spôsobuje protichodné výstupy a znižuje spoľahlivosť západky.

Obrázok 9: Logická schéma predstavuje západku S-R pomocou NOR GATE

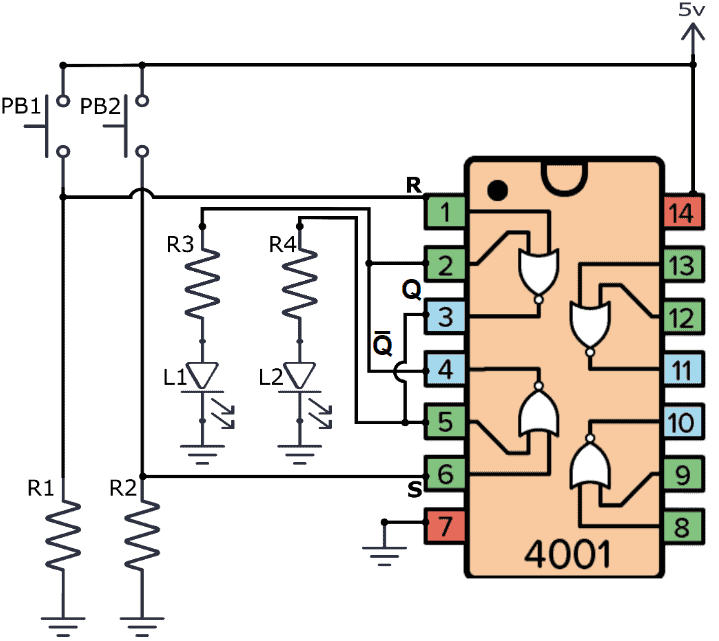

Obvod

Skúmanie, ako SR západky fungujú v skutočnom živote, ukazuje svoju užitočnosť.Dobrým príkladom je obvod s použitím čipu CD4001, ktorý má štyri ani brány.Tento obvod ukazuje, ako môžu západky SR ovládať zariadenia, ako sú LED diódy s jednoduchými akciami, ako je stlačenie tlačidiel.

V tomto príklade sú NOR Gates v čipe CD4001 nastavené na vytvorenie západky SR.Dve brány sú prepojené v slučke spätnej väzby, aby sa udržal stav západky.PushButtons sa pridávajú do obvodu ako vstupy na set a reset.Stlačením tlačidla zmení stav vstupu, ktorý mení západ a stav LED.Napríklad stlačením tlačidla Set rozsvieti LED a zostáva osvetlené aj po uvoľnení tlačidla, čo ukazuje, ako západka dokáže udržať stav.

Aby bol obvod lepší, je možné pridať viac LED diód, aby sa ukázal výstupný stav Q a Q-Bar.To uľahčuje zistenie, ako funguje západka, čo je veľmi užitočné v učebných prostrediach.

Obrázok 10: Západ S-R pomocou čipu CD4001

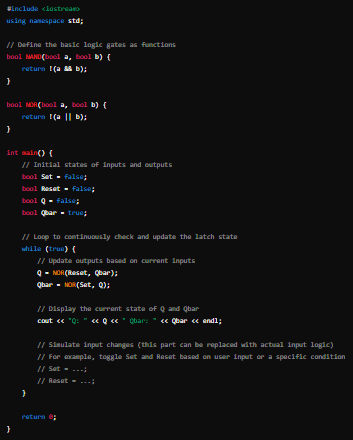

Implementácia kódu

Preklad operačnej logiky západky SR do softvéru ukazuje, ako môže dizajn digitálnej logiky fungovať vo virtuálnych aj virtuálnych simuláciách.Používanie programovacieho jazyka, ako je C ++, je efektívne, pretože podporuje zložitú logiku a kontrolu potrebnú na napodobňovanie hardvérového správania.

Ak chcete urobiť západku SR v C ++, začnete tým, že definujete základné logické brány ako funkcie, ktoré pôsobia ako ich hardvérové verzie.Napríklad funkcia brány NAND by vrátila opak a prevádzku na svojich vstupoch.Podobne by funkcia NOR GATE vrátila opak alebo operácie.S týmito základnými funkciami môžete modelovať správanie SR LATCH vytvorením slučky spätnej väzby medzi týmito funkciami brány na základe diagramu zapojenia zámky.

Kód by mal zvyčajne slučku, ktorá nepretržite kontroluje stavy vstupov (nastavená a reset) a podľa toho aktualizuje výstupy (q a q-bar).Podmienené príkazy vo vnútri tejto slučky určujú, ako zmeny vstupu ovplyvňujú výstupy, čo úzko napodobňuje fyzické správanie SR Latch.Napríklad, ak sú nastavené aj resetované vstupy nízke, výstupy zostávajú rovnaké.Ak je set vysoký a reset je nízky, výstup Q sa stáva vysokým a Q-Bar je nízka, čím sa replikuje stav nastavenia západky.

Tu je jednoduchý príklad toho, ako by to mohlo vyzerať v kóde:

Obrázok 11: SR západka v C ++

Tento kód nastaví jednoduchú západku SR pomocou brány NOR a nepretržite kontroluje a aktualizuje stav západky na základe vstupov.

Aplikácie SR západky

Riadiace systémy v operáciách motorov: SR západka požadovaná systémami pre riadenie motora.Pomocou spínačov Start (S) a Stop (R) udržuje SR západka spustená motor spustená aj po uvoľnení tlačidla Štart.Toto nastavenie zaisťuje, že motor beží nepretržite, až kým nezastaví bezpečnosť a pohodlie.

Ukladanie pamäte a dát: Pri vytváraní väčších pamäťových obvodov hrá SR západka úlohu, pretože môže ukladať jeden kúsok údajov.Udržiava údaje v stabilnom stave, až kým sa neaktualizujú, čím tvoria základ pamäťových buniek v digitálnom výpočte.

Riadenie a správa signálu: V aplikáciách riadiaceho signálu majú SR západky špecifické bity, kým nie sú splnené určité podmienky, čo zabezpečuje správnu sekvenciu a načasovanie v operáciách.Presnosť pri spracovaní signálu a toku údajov od toho závisí.

Odhadovacie obvody: SR západky stabilizujú signály z mechanických spínačov a tlačidiel, ktoré bránia falošnému spusteniu a chybám spôsobeným „odrazom“ pri stlačení prepínačov.Toto je obzvlášť vhodné do digitálnych rozhraní, ako sú klávesnice.

Základné prvky v digitálnych systémoch: Návrh žabiek a počítadiel, ktoré sú vhodné na načasovanie a sekvenovanie elektroniky, sa vo veľkej miere spolieha na západky SR.Používajú sa tiež ako pulzné západky na rýchle prepínanie stavu.

Špecializované aplikácie: V asynchrónnych systémoch sa variácie, ako je západka D, používajú na bezpečný a spoľahlivý prenos údajov.V synchrónnych dvojfázových systémoch znižujú počet západiek dát, zlepšuje účinnosť a zníženie oneskorenia.

Širšie dôsledky v elektronike: SR západky sa široko používajú v obvodoch s elektrickými zariadeniami, ktoré zohrávajú úlohu pri ochrane energie v elektronických zariadeniach.Spravujú energetické štáty na podrobnej úrovni a prispievajú k celkovej energetickej účinnosti digitálnych systémov.

Záver

Západka S-R ukazuje dôležitosť jednoduchých logických štruktúr v zložitých digitálnych systémoch.Pri pohľade na rôzne nastavenia a to, ako to funguje, vidíme, že západka S-R udržuje údaje stabilné a robí systémy efektívne a spoľahlivé.Môže fungovať za rôznych podmienok, ktoré sú zobrazené tabuľkami pravdy a logickými diagramami, vďaka čomu je prispôsobivé pre niekoľko použití, od riadenia motora až po základné digitálne obvody, ako sú žabky a počítadlá.Západka S-R je vhodná v mnohých praktických aplikáciách, ako sú pamäťové bunky v počítačoch a demontáž obvodov v digitálnych rozhraniach, zvyšujú účinnosť a znižujú chyby v elektronických zariadeniach.Vďaka mechanizmom spätnej väzby a starostlivým riadením vstupných signálov je západka S-R v poriadku na navrhovanie spoľahlivejších a efektívnejších digitálnych systémov.Štúdium jeho funkcie prostredníctvom softvérových simulácií pomáha spájať teoretickú elektroniku s aplikáciami v reálnom svete, vďaka čomu je západka S-R dôležitou témou pre nových aj skúsených elektronických inžinierov.

Často kladené otázky [FAQ]

1. Aký je účel západky SR?

Západka SR sa používa na ukladanie jedného kúska údajov;Je to základná forma pamäte v digitálnych obvodoch.Jeho hlavnou funkciou je zachovať stav trochu, kým sa nezmení vstupnými signálmi.

2. Je SR západka aktívna alebo nízka?

Západka SR je zvyčajne aktívna vysoká, čo znamená, že reaguje na vysoké vstupy (logická úroveň 1).Ak sú vstupy S (set) a R (reset) vysoké, spustia zmeny vo výstupe.

3. Aká je nevýhoda so západkou SR?

Hlavnou nevýhodou západky SR je jej náchylnosť na neplatný stav, v ktorom sú vstupy nastavené aj resetovanie vysoké súčasne.Táto situácia vedie k nedefinovanému výstupu, ktorý môže viesť k nespoľahlivému alebo nepredvídateľnému správaniu.

4. Aké sú pravidlá pre západku SR?

Ak je S (set) vysoký a R (reset) je nízky, výstup Q je nastavený na vysoký.

Ak je R vysoký a S je nízky, výstup Q sa resetuje na nízku.

Ak sú S a R nízke, výstup si zachováva svoj predchádzajúci stav.

Ak sú S a R vysoké, výstup je nedefinovaný alebo neplatný.

5. Čo je to pamäť v SR Latch?

Pamäť v západke SR sa vzťahuje na jej schopnosť udržiavať výstupný stav (vysoký alebo nízky) neurčito, až kým nedostane vstup na zmenu stavu.Vďaka tomu je bistabilné zariadenie, ktoré je ideálne pre jednoduché ukladanie pamäte.

6. Aké sú výstupy západky SR?

SR západka má dva výstupy, q a q '(q-bar).Q predstavuje súčasný stav, zatiaľ čo Q 'je inverzia Q. Keď je Q vysoký, Q' je nízky a naopak.

7. Kde používame západku?

Ak sú potrebné krátkodobé ukladanie údajov alebo uchovávanie štátu, západky sa používajú v rôznych druhoch aplikácií.Zahŕňa to ukladanie údajov v žabkách, registroch a pamäťových jednotkách, ako aj v systémoch vyžadujúcich synchronizáciu údajov a funkcie držania obvodov.

O nás

ALLELCO LIMITED

Čítaj viac

Rýchly dopyt

Zašlite prosím dotaz, okamžite odpovieme.

Statická elektrina

na 2024/06/19

Chrbtica elektrických systémov: komplexný sprievodca usmerňovačmi

na 2024/06/17

Populárne príspevky

-

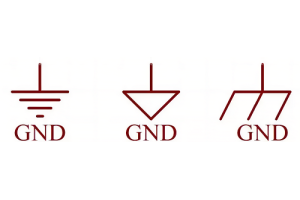

Čo je GND v okruhu?

na 1970/01/1 2944

-

Sprievodca konektormi RJ-45: RJ-45 CONFORKÁLNE FARBY KÓDY, SYSTÉMY PREVÁDZKY, APLIKÁCIE R-J45, RJ-45 DATASHEETY

na 1970/01/1 2501

-

Typy konektorov vlákien: SC vs LC a LC vs MTP

na 1970/01/1 2089

-

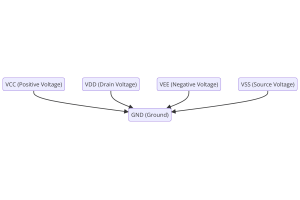

Pochopenie napájacieho napätia v elektronike VCC, VDD, VEE, VSS a GND

na 0400/11/9 1895

-

Porovnanie DB9 a RS232

na 1970/01/1 1765

-

Čo je batéria LR44?

Elektrina, ktorá všadeprítomná sila, ticho preniká každý aspekt nášho každodenného života, od triviálnych pomôcok až po život ohrozujúce lekárske vybavenie, zohráva tichú úlohu.Skutočné uchopenie tejto energie, najmä to, ako ju ukladať a efektívne na výstupe, však nie je ľahká úloha.Na tomto pozadí sa tento článok zameriava na typ batérie Coin Cell, ktorá sa mô...na 1970/01/1 1714

-

Pochopenie základov: odpor indukčnosti a kapacita

V zložitom tanci elektrotechniky sa trojica základných prvkov dostáva do centra pozornosti: indukčnosť, odpor a kapacita.Každý nesie jedinečné vlastnosti, ktoré diktujú dynamické rytmy elektronických obvodov.Tu sa vydáme na cestu, aby sme dešifrovali zložitosť týchto komponentov, aby sme odhalili ich zreteľné úlohy a praktické využitie v rozsiahlom elektrickom orchestri.Ind...na 1970/01/1 1657

-

Komplexný sprievodca batériou CR2430: Špecifikácie, aplikácie a porovnanie s batériami CR2032

Čo je batéria CR2430?Výhody batérií CR2430NormaAplikácie batérií CR2430CR2430 ekvivalentCR2430 vs CR2032Veľkosť batérie CR2430Čo hľadať pri nákupe CR2430 a ekvivalentovDátový list PDFČasto kladené otázky Batérie sú srdcom malých elektronických zariadení.Medzi mnohými dostupnými typmi zohrávajú mince bunky rozhodujúcu úlohu, ktorá sa bežne vyskytuje v kalkulačkách...na 1970/01/1 1556

-

Čo je RF a prečo ho používame?

Technológia rádiových frekvencií (RF) je kľúčovou súčasťou modernej bezdrôtovej komunikácie, ktorá umožňuje prenos údajov na veľké vzdialenosti bez fyzických pripojení.Tento článok sa ponorí do základov RF a vysvetľuje, ako elektromagnetické žiarenie (EMR) umožňuje RF komunikáciu.Preskúmame princípy EMR, stvorenie a kontrolu signálov RF a ich rozsiahle využitie.Te...na 1970/01/1 1543

-

CR2450 vs CR2032: Dá sa namiesto toho použiť batéria?

Lítiové mangánové batérie majú určité podobnosti s inými lítiovými batériami.Vysoká hustota energie a dlhá životnosť sú vlastnosti, ktoré majú spoločné.Tento druh batérie získal dôveru a láskavosť mnohých spotrebiteľov kvôli svojej jedinečnej bezpečnosti.Drahé technické prístroje?Malé spotrebiče v našich domovoch?Rozhliadnite sa a uvidíte ich všade.Medzi tým...na 1970/01/1 1513