Mastering SR západky: symboly, funkcie a praktické aplikácie

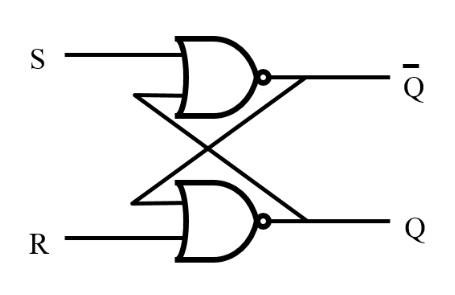

Západka SR je asynchrónny obvod, ktorý pracuje nezávisle od hodinových signálov, čo z neho robí všestranný nástroj v rôznych aplikáciách.Udržiava binárny stav - buď vysoký (1) alebo nízky (0) - a môže uložiť jediný kúsok informácií, ktoré drží, kým nové vstupné signály nepredvídajú zmenu.Tento základný prvok binárneho úložiska je skonštruovaný pomocou dvoch krížových logických brán, zvyčajne ani brány NAND.Nastavený vstup (S) aktivuje západku, nastavenie výstupu (Q) na vysoký, zatiaľ čo resetový vstup (R) nastavuje výstup na nízky.Súčasné vysoké signály na oboch vstupoch však vedú k nedefinovanému stavu, dizajnéri stavu sa musia vyhnúť.SR západky nie sú len teoretické konštrukty;Sú implementované v praktických systémoch na uchovávanie dočasných údajov, podporu výsledkov stredného spracovania a dokonca riadenie detekcie chýb v kritických aplikáciách, ako je letectvo a zdravotnícke pomôcky, a predstavujú ich nevyhnutnosť v návrhu digitálnych obvodov.Katalóg

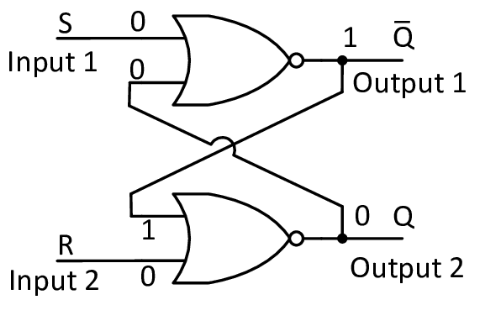

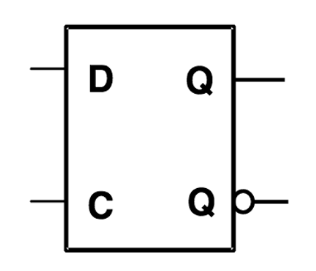

Obrázok 1: Sr západka

Čo je to SR západka?

Západná západka SR alebo západka nastavená je základným prvkom binárneho úložného priestoru, ktorý patrí do kategórie asynchrónnych obvodov.Na rozdiel od synchrónnych obvodov pracujú SR západky bez hodinového signálu a spoliehajú sa výlučne na priame ovládanie vstupných signálov.To im umožňuje fungovať nezávisle v rámci digitálnych obvodov.Západka SR môže udržiavať dva stabilné stavy: vysoká (1) a nízka (0), čo jej umožňuje ukladať jeden kúsok informácií, kým sa neaktualizuje novými vstupnými signálmi.

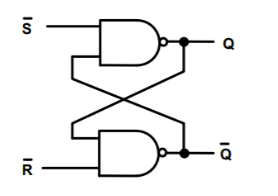

Konštrukcia západky SR zvyčajne zahŕňa dve krížové logické brány, bežne ani brány alebo brány NAND.Pri návrhu SR západky s použitím NOR Gates je výstup každej brány pripojený k vstupu druhej, čím sa vytvára spätná väzba.Táto konfigurácia zaisťuje, že západka môže rýchlo meniť stavy na základe vstupných signálov pri zachovaní stability, až kým nový vstup nezvinie zmenu.

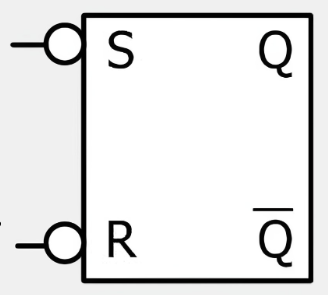

Obrázok 2: SR západka (2)

Nastavte vstupy (S): Keď je nastavený vstup (S) aktivovaný (vysoký), výstup západky (Q) sa prepína na vysoký (1).

Reset vstupu (r): Keď je aktivovaný resetový vstup (r) (vysoký), výstup (q) prepne na nízku (0).

Oba vstupy vysoké: Ak sú vstupy S a R vysoké súčasne, západka vstupuje do nedefinovaného stavu, ktorému by sa malo vyhnúť dizajnu.

SR západky sú nevyhnutné pre dočasné ukladanie údajov a stredný výsledok v digitálnych systémoch.Sú to základné prvky v zložitejších sekvenčných obvodoch, ako sú viac-bitové radiace registre, pamäťové jednotky a určité typy počítadiel.

V týchto aplikáciách poskytujú západky SR stabilné uchovávanie údajov a môžu rýchlo reagovať na zmeny externých signálov, čím sa zabezpečí efektívna prevádzka celého elektronického systému.

Ďalšou kritickou aplikáciou SR západky je detekcia chýb a korekcia v digitálnych obvodoch.Kvôli svojej schopnosti držať stabilný stav môžu monitorovať zmeny stavu systému a rýchlo sa po zistení anomálie rýchlo vrátiť do preddefinovaného bezpečného stavu.Táto vlastnosť je obzvlášť cenná v systémoch s vysokou spoľahlivosťou, ako sú letecké a zdravotnícke pomôcky.

Symbol západky SR

Pochopenie jeho symbolu a štruktúry je zásadné pre pochopenie jeho prevádzky a praktického využívania.V diagramoch obvodu má SR západka zvyčajne dva hlavné vstupné porty označené S (set) a R (reset).Tieto vstupy riadia výstupný stav západky, bežne znázornený ako Q. Niektoré vzory obsahujú aj inverzný výstup označený Q ', ktorý poskytuje opačný stav Q.

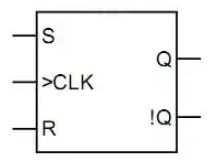

Obrázok 3: Symbol západky SR

Západka SR je často znázornená obdĺžnikovým symbolom so vstupmi S a R a výstupom Q. V niektorých prípadoch je tiež zobrazený výstup Q '.Toto jasné označenie umožňuje návrhárom obvodov rýchlo identifikovať funkciu komponentu a jej úlohu vo väčšom obvode.

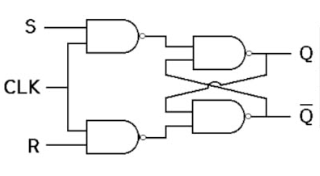

Spoločný variant západky SR obsahuje vstup hodín (CLK).Vstup CLK zaisťuje, že zmeny stavu sa vyskytnú v synchronizácii s hodinovým signálom, čo umožňuje presné riadenie načasovania.V tomto nastavení, aj keď je aktivovaná S alebo R, stav západky sa aktualizuje iba vtedy, keď signál CLK spĺňa konkrétne podmienky, zvyčajne na stúpajúcom alebo klesajúcom okraji.Tým sa zabraňuje chybám spôsobeným závadami vstupného signálu alebo nezamýšľanými zmenami.

Obrázok 4: Symbol hodinovej západky SR

Symbol SR -SR Symbol SR obsahuje vstupy S, R a CLK vo vnútri obdĺžnika.Táto štandardizovaná reprezentácia pomáha dizajnérom pochopiť funkčnosť zámky a jej požiadavky na časovanie.Napríklad vo vysokovýkonných výpočtových systémoch alebo komplexných systémoch prenosu údajov, starostlivá kontrola CLK zaisťuje ukladanie a presné ukladanie údajov v každej fáze spracovania, čím sa optimalizuje celkový výkon a spoľahlivosť systému.

Presná kontrola vstupov SR západky je dôležitá, najmä pri navrhovaní vysokorýchlostných a veľkokapacitných pamäťových alebo dočasných dátových vyrovnávacích pamätí.Navrhovaním logických obvodov na správu aktivácie S a R je možné dosiahnuť zložité funkcie, ako je načítavanie údajov, zúčtovanie alebo resetovanie stavu.Presná kontrola signálu CLK zaisťuje, že všetky operácie údajov sledujú preddefinovanú časovaciu sekvenciu, čo výrazne zvyšuje účinnosť systému a schopnosť spracovania údajov.

Hlboké pochopenie symbolu a štruktúry SR LATCH pomáha nielen v správnom návrhu obvodov a riešení problémov, ale aj pri vykonávaní komplexných digitálnych logických operácií a zlepšovaní výkonu systému.Toto je obzvlášť dôležité v aplikáciách, ktoré si vyžadujú vysokú spoľahlivosť a presnú kontrolu, ako sú letecké a zdravotnícke pomôcky.

Typy západiek a ich pracovné princípy

Zápasy sú základnými komponentmi v elektronickom dizajne a ponúkajú rôzne funkcie a široké aplikácie.Hlavnými typmi západiek sú západky SR a d za západky, z ktorých každá má jedinečné operácie a prípady použitia.

Zachytávanie SR

Západná západka SR alebo západka nastavenia je základným úložným zariadením riadeným jeho dvoma vstupmi, S (set) a R (reset).

Keď vstup S dostane vysoký signál, výstup Q sa stane vysokým, čo naznačuje, že údaje sú nastavené.Keď vstup R dostane vysoký signál, výstup Q je nízky, čo naznačuje, že údaje sa obnovia.Ak sú vstupy S a R vysoké súčasne, západka vstupuje do nedefinovaného stavu, čo spôsobuje potenciálnu nestabilitu výstupu.Tomuto stavu sa musí vyhnúť dizajnu.Priama reakcia SR Latch na vstupné signály robí užitočnú v situáciách, ktoré si vyžadujú rýchlu reakciu.

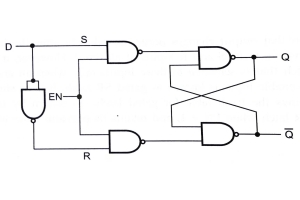

D západka

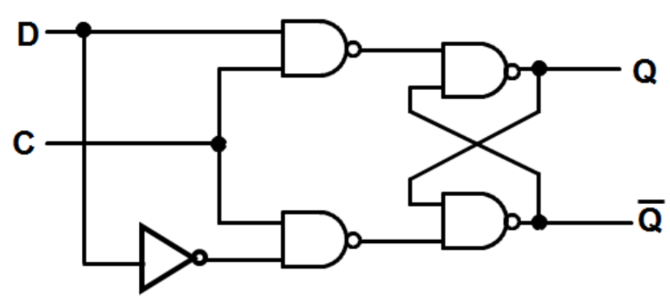

Západka D, známa tiež ako dátová západka alebo priehľadná západka, ponúka zložitejšiu kontrolu s vstupom údajov D a CLOCK SIGNAL CLK.

Obrázok 5: D Západka

Obrázok 6: symbol západky

Keď je CLK vysoký, výstup Q sa riadi vstupom D, čo umožňuje údajom voľne prechádzať cez západku.Keď CLK klesne, aktuálna hodnota D je uzamknutá a výstup Q zostáva konštantný až do nasledujúceho vysokého signálu CLK.Vďaka tomuto mechanizmu je Dlátka D ideálna na dočasné ukladanie údajov na synchronizáciu rôznych rýchlosti spracovania v systéme.

Západky SR a D majú jedinečnú úlohu pri ukladaní údajov a logike stavu strojov.Vďaka svojej priamej reakcii na úroveň vstupu sú západky nevyhnutné pri navrhovaní asynchrónnych obvodov.Poskytujú životne dôležité funkcie pre zložité prenosy údajov a systémy na správu energie, čím efektívne ukladajú štátne informácie, aby sa zabezpečila stabilná prevádzka.Správne používanie týchto západiek môže významne zlepšiť spoľahlivosť a účinnosť obvodov, čo ich robí nevyhnutnými v moderných elektronických systémoch.

Tabuľka pravdy SR západky

Obrázok 7: Sr Nand Latch

|

Siež |

R |

Otázka |

Q ' |

Poznámka |

|

0 |

0 |

1 |

1 |

Zakázaný |

|

0 |

1 |

1 |

0 |

Súbor |

|

1 |

0 |

0 |

1 |

Vynulovanie |

|

1 |

1 |

Otázka |

Q ' |

Udržať si |

Graf 1: Tabuľka pravdy SR Latch s použitím nand brány

Obrázok 8: SR ani západka

|

Siež |

R |

Otázka |

Q ' |

Poznámka |

|

0 |

0 |

Otázka |

Q ' |

Udržať si |

|

0 |

1 |

1 |

0 |

Vynulovanie |

|

1 |

0 |

0 |

1 |

Súbor |

|

1 |

1 |

0 |

0 |

Zakázaný |

Graf 2: Tabuľka pravdy SR Latch Použitie NOR -GATES

Teraz berieme tabuľku pravdy o SR západke, ktorá používa ako príklad, aby sme pochopili význam tabuľky pravdy SR západky.

Vstupné a výstupné stavy

S a R sú 0: západka zostáva v súčasnom stave.Výstup Q zostáva rovnaký, či už je 0 alebo 1.

S je 0 a R je 1: západka resetov, čo núti výstup Q na 0.

S je 1 a r je 0: Sada západiek, vďaka čomu je výstup Q rovný 1.

S a R sú 1: Táto podmienka je neplatná alebo nedefinovaná, často označovaná ako „zakázaný“ stav v západke SR.V tomto prípade q a q 'rovnaké 0, čo vedie k nejednoznačnému výstupu.

Keď sú S a R 0, západka nerobí nič a jednoducho drží svoju aktuálnu hodnotu.Je to užitočné pri udržiavaní štátu bez zmien.

Ak je S 0 a R 1, je výslovne povedané, že západka je výslovne povedaná, aby sa ubezpečilo, že Q je 0 0 bez ohľadu na predchádzajúci stav.Toto je jednoduchý spôsob, ako vyčistiť západku.

Keď je S 1 a R je 0, západka je nastavená, čím sa zaistí, že Q sa stane 1. Takto ukladáte „1“ v západke.

Ak sú S a R 1, štát nie je povolený, pretože spôsobuje, že obidva výstupy sú 0, čo je protichodné a nespoľahlivé.Dizajnéri sa musia vyhnúť tejto podmienke, aby zabezpečili stabilnú prevádzku.

Výhody a nevýhody západiek

Západky sa široko používajú pri dizajne digitálnych obvodov kvôli ich jednoduchosti a nízkym nákladom.Tieto charakteristiky umožňujú západkám fungovať pri vysokej rýchlosti s nízkou spotrebou energie, vďaka čomu sú ideálne pre vysokorýchlostné digitálne systémy.Napríklad v súboroch registrov procesorov môžu západky rýchlo ukladať a načítať údaje, čo výrazne zvyšuje rýchlosť a efektívnosť spracovania.

Výhody západiek

Jednoduchosť a nákladová efektívnosť: západky sú jednoduché komponenty, ktoré sú lacné implementovať v digitálnych obvodoch.

Vysoká rýchlosť a nízka energia: Ich dizajn umožňuje rýchlu prevádzku s minimálnou spotrebou energie, ktorá je kritická v vysokorýchlostných digitálnych systémoch.

Účinnosť pri spracovaní údajov: V aplikáciách, ako sú súbory registrov procesorov, poskytujú západky rýchle ukladanie údajov a získavanie, čím sa zvyšuje celkový výkon systému.

Nevýhody západiek

Napriek ich výhodám majú západky pozoruhodné obmedzenia v určitých dizajnoch a aplikáciách.

Neočakávateľné správanie v asynchrónnych dizajnoch: Bez riadenia signálu hodín sa západky môžu správať nepredvídateľne.V západkách SR, ak sú vstupy set (s) aj reset (R) vysoké súčasne, výstup sa stane nedefinovaný, čo vedie k nestabilite.Toto je problematické v regulácii v reálnom čase alebo v aplikáciách kritických bezpečnostných podmienok, kde je spoľahlivý výstup rozhodujúci.

Komplexný dizajn načasovania: Návrh s západkami si vyžaduje starostlivé úvahy očasovania.Inžinieri musia zodpovedať za oneskorenia šírenia signálu a podmienky pretekov, aby sa predišlo chybám načasovania.Nesprávny návrh môže viesť k zmenám údajov skôr, ako sa stabilizuje signál hodín, čo spôsobí korupciu údajov alebo nesprávne zachytenie údajov.To si vyžaduje hlboké pochopenie analýzy načasovania a správania obvodu.

Na riešenie týchto výziev je možné použiť špecifické techniky a stratégie navrhovania:

Synchronizačné mechanizmy: Pridanie synchronizačných mechanizmov môže pomôcť zvládnuť asynchrónne vstupy a zmierniť nepredvídateľné správanie.

Vlastná správa hodín: Implementácia prispôsobených stratégií správy hodín môže zabezpečiť, aby boli údaje správne a v pravý čas.

Používanie nástrojov EDA: Nástroje Modern Electronic Design Automation (EDA) ponúkajú pokročilé analýzy a optimalizačné možnosti.Tieto nástroje pomáhajú predpovedať a riešiť problémy s načasovaním a synchronizáciou počas fázy návrhu, čím sa zlepšuje spoľahlivosť a výkon digitálnych systémov pomocou západiek.Pomáhajú dizajnérom pri včasnom identifikácii potenciálnych problémov a zaisťujú, že konečný produkt funguje spoľahlivo za rôznych podmienok.

Praktické aplikácie SR západky

SR západky, známe svojou schopnosťou rýchlo a spoľahlivo udržiavať stav, sa široko používajú v rôznych elektronických systémoch.Vynikajú v scenároch vyžadujúcich dočasné ukladanie údajov alebo zadržiavanie štátu.

Dočasné ukladanie údajov

SR západky sa často používajú v pamäti vyrovnávacej pamäte na dočasné ukladanie údajov.To umožňuje systému rýchlo prístup k často používaným údajom, čo výrazne zvyšuje schopnosti spracovania údajov a efektívnosť rozsiahlych procesorov.

Úložné registrovanie súborov

V procesoroch umožňujú SR západky rýchle ukladanie a získavanie údajov v registračných súboroch, čím sa zvyšuje rýchlosť spracovania a celkový výkon systému.

Udržiavanie riadiacich signálov

V systémoch digitálneho riadenia sú západky SR užitočné pri udržiavaní stavu určitých riadiacich signálov, kým externé podmienky alebo systémová logika diktuje zmenu.Pomáhajú tiež pri zachovaní štátov v systéme a zabezpečujú konzistentný výkon v operáciách, ktoré si vyžadujú presnosť a spoľahlivosť.

Spúšťacie a protikladné obvody

Flip-flopy založené na západke SR sa bežne používajú v obvodoch vyžadujúcich synchronizovanú prevádzku, ako sú digitálne hodiny a časovače.Ovládajú počet impulzov, zabezpečujú presné časové obdobie a spoľahlivý výkon.Tieto obvody sa spoliehajú na západky SR, aby sa udržali presné počty, čo uľahčuje načasovanie a sekvenovanie v digitálnych systémoch.

Mechanické interakcie

SR západky sú účinné pri odstraňovaní mechanického odrazu v spínačoch.Mechanické odrazy nastane, keď spínač generuje rýchle opakované zmeny signálu v dôsledku slabého kontaktu.SR západky stabilizujú výstupný signál, čím bránia chybám spôsobeným hlučnými signálmi.

Žabky

Flip-flop SR, často nazývaný flip-flop vyvolaný hranou, pozostáva z dvoch vzájomne prepojených západok SR.Táto štruktúra s dvoma šnúrkami jej umožňuje reagovať na konkrétne hrany hodinových signálov (buď stúpajúcich alebo padajúcich), aby zmenila svoj stav.To sa dosahuje prostredníctvom špeciálnej logickej kontroly medzi západkami.Výstup prvej západky sa stáva súčasťou vstupu pre druhú západku a výstup druhej západky zase ovplyvňuje prvú západku a vytvára spätnú väzbu spätnej väzby.

Obrázok 7: SR Flip-Flop

Flip-flop SR mení stav presne pri stúpaní alebo klesajúcom okraji signálu hodín.Prehliadková spätná väzba medzi dvoma západkami SR zaisťuje, že flip floP mení iba stav v reakcii na hranu hodín, čím poskytuje stabilný a spoľahlivý výstup.

V mikroprocesoroch a procesoroch digitálneho signálu sa na odber vzoriek a ukladanie údajov používajú flopy SR.Zachytávajú a stabilizujú údaje na určených hranoch hodín, čím zabezpečujú spoľahlivé následné spracovanie a analýzu údajov.

Mechanizmus spúšťania okrajov pomáha vyhnúť sa podmienkam pretekov, kde rôzne časti obvodu môžu meniť stav súčasne bez synchronizácie, čo potenciálne vedie k nestabilným alebo nesprávnym výstupom.Flip-flop SR sú rozhodujúce pri implementácii špecifickej logiky komunikačného protokolu, ako je synchronizácia rámcov a detekcia chýb.Ich stabilita a rýchly čas odozvy pomáhajú udržiavať kvalitu prenosu údajov a spoľahlivosť systému.

Zakázané štáty v SR západky a žabky SR

Pri navrhovaní západiek SR a SR žabky pomocou NAND a NOR GATES musíme všetci venovať pozornosť riadeniu a vyhýbaniu sa inhibovaným štátom.Zakázaný stav sa vyskytuje, keď sú vstupy sada (s) aj reset (R) súčasne vysoké (pre brány NAND) alebo nízke (pre brány).Táto kombinácia vedie k neurčitému stavu výstupu, pretože výstup závisí od predchádzajúceho stavu obvodu, čo je nepredvídateľné.

Zakázané štáty v Nand Gate Sr Západne

Ak sú S a R nízke, oba výstupy stúpajú vysoko, čo porušuje charakteristiku doplnkovej výstupu západky.To má za následok neurčitý stav.

Zakázané štáty v NOR Gate Sr Sr.

Ak sú S a R vysoké, oba výstupy klesnú, a tiež vytvárajú neurčitý stav.To môže viesť k nepredvídateľnému správaniu v obvode.

Praktické prístupy, aby sa vyhli zakázaným štátom

Pridanie riadiacej logiky

Použite ďalšie logické brány na monitorovanie stavov S a R. Ak oba vstupy trend smerom k stavu zakázaného stavu, automaticky upravte jeden vstup tak, aby sa zabránilo neurčitému stavu.To zaisťuje, že výstupy zostanú stabilné a predvídateľné.Implementujte logickú bránu, ktorá zasahuje, keď sú S a R vysoké (alebo nízke), a upravte jeden vstup tak, aby sa udržal platný stav.

Simulácia softvéru a testovanie hardvéru

Vykonajte dôkladné simulácie softvéru na identifikáciu potenciálnych zakázaných stavov za rôznych prevádzkových podmienok.To umožňuje dizajnérom pozorovať a opraviť logické chyby pred fyzickou implementáciou.Vykonajte rozsiahle testovanie hardvéru, aby ste overili, či obvod správne spracováva všetky vstupné kombinácie.Tento krok pomáha zabezpečiť, aby zástava alebo klopný obklad fungovali spoľahlivo v scenároch v reálnom svete.

Záver

Univerzálnosť a spoľahlivosť západok SR podčiarkujú svoj význam v digitálnom obvode.Preskúmaním nuantu správania sa SR západky prostredníctvom ich symbolových reprezentácií, tabuliek pravdy a praktických aplikácií získavame komplexné pochopenie ich činnosti a dôležitosti.Napriek potenciálnym úskaliam nedefinovaných stavov v asynchrónnych dizajnoch môže tieto riziká zmierniť strategická implementácia logiky kontroly a rozsiahle simulácie.Nástroje Advanced Electronic Design Automation (EDA) ďalej zvyšujú spoľahlivosť a výkon obvodov zahŕňajúcich západky SR predpovedaním a riešením problémov s načasovaním a synchronizáciou.Či už sa používa pri dočasnom ukladaní údajov, údržbe riadiaceho signálu alebo detekcii chýb, západky SR sa ukážu ako základné pri vytváraní robustných a efektívnych digitálnych systémov.Ich úloha pri vysokorýchlostných pamäťových operáciách a synchrónnom spracovaní údajov v zložitých aplikáciách je príkladom ich trvalej relevantnosti.Ako technologický pokrok, princípy upravujúce západky SR naďalej informujú a inšpirujú inovácie v digitálnej elektronike, čo zabezpečuje, aby tieto základné komponenty zostali neoddeliteľnou súčasťou rozvoja sofistikovaných a spoľahlivých elektronických zariadení.

Často kladené otázky [FAQ]

1. Čo je to SR západka?

Západná západka SR alebo západka nastavená je základným prvkom binárneho úložiska používaného v digitálnych obvodoch.Je to asynchrónny obvod, čo znamená, že pracuje bez signálu hodín, pričom sa spolieha na priame ovládanie svojich vstupov na zmenu stavov.

2. Aká je funkcia SR v logike?

V logike vstupujú vstupy SR (Set-Reset) stav západky.

3. Aký typ logickej brány používa SR západka?

Západka SR zvyčajne používa brány ani brány alebo brány NAND.V SR Latch založenej na bráne sa výstup každej ani brány privádza späť do vstupu druhého, čím sa vytvára stabilná slučka spätnej väzby.V NAND GATE založenej na SR LATCH sa používa podobná konfigurácia spätnej väzby, ale logické úrovne sa invertujú v porovnaní s západkou NOR GATE.Obe konfigurácie dosahujú rovnakú základnú funkčnosť udržiavania binárneho stavu na základe vstupov set a reset.

4. Ako funguje západka?

Západok funguje pomocou spätnej väzby na udržanie svojho výstupného stavu na základe poskytnutých vstupov.V západke SR sú vstupy sada (s) a reset (R) riadia stav výstupu (q).Ak je nastavený vstup aktivovaný (vysoký), výstup je nastavený na vysoký (1).Ak je resetový vstup aktivovaný (vysoký), výstup sa resetuje na nízku (0).Slučka spätnej väzby v návrhu zámky zaisťuje, že akonáhle je stav výstupu stanovený, zostáva stabilný, kým ho nezmení nový vstupný signál.

5. Aká je nevýhoda so západkou SR?

Primárnou nevýhodou západky SR je nedefinovaný stav, ktorý sa vyskytuje, keď sú vstupy set (s) aj reset (R) vysoké súčasne.Táto podmienka vedie k neurčitému výstupnému stavu, ktorý môže spôsobiť nestabilitu a nepredvídateľné správanie v digitálnych obvodoch.Tomuto „zakázanému“ štátu sa musí vyhnúť návrhu, aby sa zabezpečila spoľahlivé prevádzky.

SR západka, západka nastavenia, asynchrónny obvod, prvok binárneho úložného priestoru, digitálne obvody, brány, NAND brány, slučka spätnej väzby, vysoký stav, nízky stav, nedefinovaný stav, hodinový signál, priame ovládanie, dočasné ukladanie údajov, stredné držanie výsledkov,detekcia chýb, letecké aplikácie, zdravotnícke pomôcky, návrh obvodu, kolísaná západka SR, vstupné signály, symbol a štruktúra, vysokorýchlostná pamäť, dátové vyrovnávacie pamäte, riadenie načasovania, presná kontrola, retencia stavu, mikroprocesory, procesory digitálnych signálov, vzorkovanie údajov, dáta, dátaUkladanie, spúšťané na okraji, SR Flip-FLOP, spätná väzba pre vzájomné prepojenie, podmienky pretekov, logika komunikačného protokolu, synchronizácia rámcov, detekcia chýb, chyby signálu, automatizácia elektronického dizajnu, nástroje EDA, mechanizmy synchronizácie, vlastné riadenie hodín, chyby načasovania, oneskorenia šírenia, oneskorenia, oneskorenia propagácie, oneskorenia, oneskorenia propagácie, oneskorenia, oneskorenia šírenia, oneskorenia, oneskorenia propagácie, oneskorenia propagácie,Rasové podmienky, komplexné prenosy údajov, systémy riadenia výkonu, mechanické odrazy, praktické aplikácie, systémy digitálneho riadenia, logické brány, simulácie softvéru, hardvérové testovanie, zakázané stavy, spoľahlivosť západky.

O nás

ALLELCO LIMITED

Čítaj viac

Rýchly dopyt

Zašlite prosím dotaz, okamžite odpovieme.

Sprievodca základmi D žabky - obvody, tabuľky pravdy, typy, výhody a obmedzenia

na 2024/05/17

Porovnávací sprievodca analýzou reostatu a potenciometrov

na 2024/05/17

Populárne príspevky

-

Čo je GND v okruhu?

na 1970/01/1 2943

-

Sprievodca konektormi RJ-45: RJ-45 CONFORKÁLNE FARBY KÓDY, SYSTÉMY PREVÁDZKY, APLIKÁCIE R-J45, RJ-45 DATASHEETY

na 1970/01/1 2501

-

Typy konektorov vlákien: SC vs LC a LC vs MTP

na 1970/01/1 2089

-

Pochopenie napájacieho napätia v elektronike VCC, VDD, VEE, VSS a GND

na 0400/11/9 1895

-

Porovnanie DB9 a RS232

na 1970/01/1 1765

-

Čo je batéria LR44?

Elektrina, ktorá všadeprítomná sila, ticho preniká každý aspekt nášho každodenného života, od triviálnych pomôcok až po život ohrozujúce lekárske vybavenie, zohráva tichú úlohu.Skutočné uchopenie tejto energie, najmä to, ako ju ukladať a efektívne na výstupe, však nie je ľahká úloha.Na tomto pozadí sa tento článok zameriava na typ batérie Coin Cell, ktorá sa mô...na 1970/01/1 1714

-

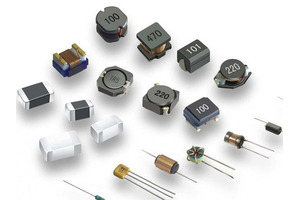

Pochopenie základov: odpor indukčnosti a kapacita

V zložitom tanci elektrotechniky sa trojica základných prvkov dostáva do centra pozornosti: indukčnosť, odpor a kapacita.Každý nesie jedinečné vlastnosti, ktoré diktujú dynamické rytmy elektronických obvodov.Tu sa vydáme na cestu, aby sme dešifrovali zložitosť týchto komponentov, aby sme odhalili ich zreteľné úlohy a praktické využitie v rozsiahlom elektrickom orchestri.Ind...na 1970/01/1 1655

-

Komplexný sprievodca batériou CR2430: Špecifikácie, aplikácie a porovnanie s batériami CR2032

Čo je batéria CR2430?Výhody batérií CR2430NormaAplikácie batérií CR2430CR2430 ekvivalentCR2430 vs CR2032Veľkosť batérie CR2430Čo hľadať pri nákupe CR2430 a ekvivalentovDátový list PDFČasto kladené otázky Batérie sú srdcom malých elektronických zariadení.Medzi mnohými dostupnými typmi zohrávajú mince bunky rozhodujúcu úlohu, ktorá sa bežne vyskytuje v kalkulačkách...na 1970/01/1 1555

-

Čo je RF a prečo ho používame?

Technológia rádiových frekvencií (RF) je kľúčovou súčasťou modernej bezdrôtovej komunikácie, ktorá umožňuje prenos údajov na veľké vzdialenosti bez fyzických pripojení.Tento článok sa ponorí do základov RF a vysvetľuje, ako elektromagnetické žiarenie (EMR) umožňuje RF komunikáciu.Preskúmame princípy EMR, stvorenie a kontrolu signálov RF a ich rozsiahle využitie.Te...na 1970/01/1 1542

-

CR2450 vs CR2032: Dá sa namiesto toho použiť batéria?

Lítiové mangánové batérie majú určité podobnosti s inými lítiovými batériami.Vysoká hustota energie a dlhá životnosť sú vlastnosti, ktoré majú spoločné.Tento druh batérie získal dôveru a láskavosť mnohých spotrebiteľov kvôli svojej jedinečnej bezpečnosti.Drahé technické prístroje?Malé spotrebiče v našich domovoch?Rozhliadnite sa a uvidíte ich všade.Medzi tým...na 1970/01/1 1512