XCV200-6FG456C FPGA: Funkcie, špecifikácie, programovanie a aplikácie

XCV200-6FG456C je výkonná FPGA (pole Field-Programmable GATE) zo série AMD Xilinx Virtex®.Táto príručka vysvetľuje jeho funkcie, rozloženie PIN, programy a použitia.Vďaka vysokému výkonu spracovania, flexibilným možnostiam dizajnu a silným možnostiam vstupu/výstupu (I/O), tento FPGA pomáha vytvárať rýchle a spoľahlivé digitálne systémy.Či už pracujete na sieťových, riadiacich systémoch alebo vlastnej elektronike, táto príručka vám pomôže pochopiť, ako sa dá vo vašich projektoch použiť XCV200-6FG456C.Katalóg

Prehľad XCV200-6FG456C

Ten XCV200-6FG456C je pozoruhodný model v rodine AMD Xilinx Virtex® FPGA, ktorý je navrhnutý tak, aby poskytoval robustné programovateľné logické riešenia pre zložité digitálne systémy.Tento špecifický čip zahŕňa približne 236 666 systémových brán a funkcií 1 176 konfigurovateľných logických blokov (CLB) a 5 292 logických buniek.Zahŕňa tiež 57 344 celkových bitov RAM a podpory 284 vstupno-výstupných kolíkov, ktoré sú umiestnené v balíku GRAL mriežky s priemerom 456 loptičiek (FBGA), merajúce 23 mm x 23 mm.Tento model pracuje na nominálnom napätí 2,5 V, s rozsahom 2,375 V až 2,625 V a môže fungovať v teplotnom rozsahu od 0 ° C až 85 ° C.Širšia séria Virtex® sa uspokojuje s celým radom aplikácií s hustotou od 50 000 do viac ako 1 milióna systémových brán a systémových hodín až 200 MHz.Podporuje okrem iného množstvo I/O štandardov vrátane LVTTL, LVCMOS a PCI.Funkcie, ako sú slučky zamknuté oneskorením (DLL), konfigurovateľné logické bloky so zabudovanou pamäťou a vyhradená logika prenášania pre aritmetické operácie, zvyšujú jeho funkčnosť.Rodina Virtex®, ktorá je vyrobená s použitím 5-vrstvového kovového procesu, zaručuje výkon a spoľahlivosť.

Ak hľadáte integráciu technológie najvyššej úrovne FPGA do vašich produktov alebo systémov, nákup XCV200-6FG456C vo veľkom s nami je inteligentným krokom.Spĺňa priemyselné normy a udržuje vás pred budúcimi technologickými potrebami.

Vlastnosti XCV200-6FG456C

• Systémové brány: XCV200-6FG456C ponúka približne 236 666 systémových brán.Tento vysoký počet brán umožňuje implementáciu komplexných integrovaných digitálnych logických obvodov na jednom čipe, čím sa zvýši výkon a všestrannosť v rôznych aplikáciách.

• Logické zdroje: Zahŕňa 1 176 konfigurovateľných logických blokov (CLB) a 5 292 logických buniek.Tieto zdroje sú dobré na navrhovanie flexibilných a škálovateľných digitálnych obvodov.CLB je možné naprogramovať tak, aby vykonávali širokú škálu logických funkcií, zatiaľ čo veľké množstvo logických buniek umožňuje spracovanie rozsiahlych logických operácií a procesov.

• Pamiatka: Zariadenie poskytuje 57 344 bitov pamäte RAM, ktoré sú rozdelené medzi svoje logické bloky.Tento zabudovaný RAM sa používa pre aplikácie, ktoré vyžadujú rýchle a efektívne ukladanie a získavanie údajov, čo podporuje vysokorýchlostné dátové operácie neoddeliteľnou súčasťou moderných digitálnych systémov.

• I/O schopnosti: S 284 vstupnými/výstupnými kolíkmi, XCV200-6FG456C uľahčuje rozsiahle možnosti prepojenia.Tieto I/O PIN podporujú rôzne štandardy signálu a umožňujú FPGA efektívne komunikovať s inými komponentmi v systéme, ako sú pamäťové zariadenia, procesory a periférie.

• Rozsah napätia a teploty: Pracujúca pri nominálnom napätí 2,5 V, s prijateľným rozsahom od 2,375 V do 2,625 V, je tento FPGA navrhnutý na spotrebu nízkej energie pri zachovaní robustného výkonu.Môže fungovať v rámci teplotného rozsahu spojky od 0 ° C až 85 ° C, čím sa zabezpečí spoľahlivosť za rôznych podmienok prostredia.

XCV200-6FG456C funkčný diagram PIN

Ten XCV200-6FG456C funkčný diagram PIN je štruktúrovaná reprezentácia priradení PIN FPGA, ktoré sú rozdelené do rôznych bánk (Banka 0 až banka 7).Každá banka zoskupuje kolíky na základe ich funkcie a fyzického umiestnenia na balíku FPGA.Systém čísla a označovania sleduje vzor mriežky, kde sú riadky označené písmenami (A, B, C atď.) A stĺpcami podľa čísel (1, 2, 3 atď.), Ktoré uľahčujú rýchlu identifikáciu konkrétnych kolíkov.Tieto banky zodpovedajú rôznym vstupným/výstupným funkciám, výkonu, zemi a vyhradeným smerovaním signálu.PINS sú priradené rôzne funkčné zoskupenia, vrátane všeobecných I/O (GPIO), často označovaných ako „G“ (všeobecný vstup/výstup), „V“ (napájanie napätia) a „O“ (výstup).Výkon a mleté kolíky sú výrazne označené, čo zabezpečuje stabilnú prevádzku FPGA.Špeciálne špendlíky, ako sú vstupy hodín, resety a ovládacie signály, sú identifikované so symbolmi ako „R“ alebo „T.“Niektoré špendlíky tiež slúžia špecializovaným komunikačným rolám, vrátane konfigurácie JTAG a vysokorýchlostného prekladania, pre programovanie a ladenie.

XCV200-6FG456C Bloková schéma

Vstupný/výstupný blok

Diagram predstavuje Vstupný/výstupný blok (IOB) Štruktúra FPGA XCV200-6FG456C, ktorá je členom rodiny Xilinx Virtex.Diagram predstavuje kľúčové prvky zapojené do vstupných a výstupných operácií, pričom zdôrazňuje tok dát a mechanizmy riadenia.V jadre diagramu sa na registráciu signálov pre vstupné, výstupné a tri-state riadenie používajú tri žabky D.Výstupný register je riadený signálom OCE (Enable Clock Enable), ktorý určuje, kedy sú výstupné údaje zaistené.Podobne je register Tri-State riadený pomocou TCE (povoľuje sa Tri-State Clock), ktorý umožňuje alebo deaktivuje výstupnú vyrovnávaciu pamäť.Vstupný register zachytáva prichádzajúce údaje a pred odovzdaním logiky FPGA prostredníctvom IBUF (vstupná vyrovnávacia pamäť) aplikuje programovateľné oneskorenie.OBUFT (výstupný vyrovnávací pamäť Tri-State) zaisťuje, že FPGA môže buď riadiť signál na podložku (I/O PIN), alebo ho umiestniť do stavu s vysokou impedanciou v závislosti od riadiacej logiky.Na podložke je zahrnutý slabý obvod strážcu, ktorý udržiava posledný známy logický stav, keď nie je prítomný žiadny aktívny vodič, čo bráni nezamýšľaným plávajúcim podmienkam.Referenčné napätie (VREF) sa používa pre určité vstupné normy, ako je SSTL alebo HSTL, ktoré vyžadujú presné úrovne napätia pre správnu prevádzku.Celkovo táto štruktúra IOB umožňuje FPGA spravovať vysokorýchlostný prenos údajov, podporovať rôzne I/O štandardy a poskytovať flexibilné riadenie načasovania a integrity signálu.

Sériový režim Master/Slave

Ten Sériový režim Master/Slave Bloková schéma ilustruje konfiguračný proces Virtex FPGA, konkrétne XCV200-6FG456C, keď je naprogramovaný v konfigurácii Daisy Chain pomocou sériového EEPROM (XC1701L).V tomto nastavení jedno zariadenie Virtex pracuje ako hlavný, riadenie konfiguračných hodín (CCLK) a sériovo prenos konfiguračných údajov na ďalšie Slave FPGA v reťazci.Master FPGA iniciuje proces konfigurácie presadzovaním signálu programu a resetuje všetky zariadenia v reťazci.Po dokončení inicializácie signál inicita označuje pripravenosť a konfiguračné dáta toky zo sériového EEPROM (XC1701L) do PIN DIN (DATA IN) PIN MASTER FPGA.Master FPGA číta údaje z EEPROM a posiela ich prostredníctvom DOUT (DATA OUT) do následného SLAVE FPGAS, synchronizuje prenos údajov pomocou signálu CCLK.Signál Hotovo sa používa na označenie úspešnej konfigurácie, pričom voliteľný odpor s vytiahnutím zabezpečuje stabilný vysoký stav po dokončení konfigurácie.XC1701L EEPROM je riadený hlavným FPGA pomocou signálov CLK, Data, CE (Enable) a Reset/OE (výstupný), čím sa zabezpečuje správne získanie uložených konfiguračných údajov.Táto metóda konfigurácie je efektívna na programovanie viacerých FPGA pomocou jedného EEPROM, znižovania zložitosti externého zapojenia a zabezpečenie všetkých zariadení prijíma synchronizované konfiguračné údaje.

Špecifikácie XCV200-6FG456C

|

Typ |

Parameter |

|

Výrobca |

Amd xilinx

|

|

Séria |

Virtex® |

|

Balenie |

Podnos |

|

Stav |

Zastaraný |

|

Počet laboratórií/CLB |

1176 |

|

Počet logických prvkov/buniek |

5292 |

|

Celkový baranový kúsok |

57344 |

|

Počet I/O |

284 |

|

Počet brán |

236666 |

|

Napätie - napájanie |

2,375V ~ 2,625V |

|

Montáž |

Povrchová montáž |

|

Prevádzková teplota |

0 ° C ~ 85 ° C (TJ) |

|

Balenie |

456-bbga |

|

Balík dodávateľských zariadení |

456-FBGA (23x23) |

|

Základné číslo produktu |

XCV200 |

Aplikácie XCV200-6FG456C

Telekomunikácie a vytváranie sietí

XCV200-6FG456C vyniká v telekomunikačných a sieťových aplikáciách vďaka svojej schopnosti zvládnuť vysokorýchlostné prenosy údajov a zložité úlohy spracovania signálu.Jeho vysoký počet brán a robustné I/O schopnosti umožňujú podporovať funkcie, ako je spracovanie paketov, modulácia/demodulácia signálu a protokoly korekcie chýb.

Spracovanie digitálneho signálu (DSP)

Tento FPGA, ktorý je ideálny pre aplikácie DSP, môže vykonávať rýchle a zložité matematické výpočty požadované pri technológiách zvuku a spracovania videa.Či už ide o multimediálne systémy, rozpoznávanie hlasu alebo streamovanie služieb, výkonné schopnosti spracovania XCV200-6FG456C a vnorená pamäťová podporujú efektívne a kvalitné spracovanie signálu.

Priemyselné riadiace systémy

V priemyselnej automatizácii poskytuje XCV200-6FG456C potrebný výkon na správu riadiacich systémov a automatizačných sietí.Jeho schopnosť vykonávať súčasne viacero riadiacich úloh a zároveň zabezpečiť, aby časy odozvy boli vhodné pre aplikácie v procese riadenia procesu, robotike a strojovom videní.

Lekárske nástroje

Presnosť a rýchlosť FPGA sú skvelé v lekárskom zobrazovacích a diagnostických zariadeniach, kde pomáha pri spracovaní zložitých algoritmov pre zobrazovacie aplikácie, ako sú MRI, ultrazvuk a CT skenovanie.Schopnosti XCV200-6FG456C zabezpečujú, že dokáže zvládnuť priepustnosť vysokej dát a zložité spracovanie požadované v moderných lekárskych technológiách.

XCV200-6FG456C Podobné časti

XCV200-6FG456C Programovacie kroky

Programovacie kroky pre XCV200-6FG456C:

1. Návrh

Počiatočná fáza programovania FPGA zahŕňa definovanie digitálnej logiky a funkčnosti vášho systému.To sa dá urobiť pomocou hardvérových popisov Languages (HDLS), ako je VHDL alebo Verilog, kde píšete kód, ktorý určuje, ako FPGA spracováva údaje a interaguje s iným hardvérom.Schematické vstupné nástroje dostupné v dizajnérskom softvéri FPGA, ako je Xilinx ISE alebo Vivado, je možné využiť.Táto metóda zahŕňa vytvorenie vizuálnej reprezentácie logiky presúvaním a vyhodením komponentov, ktoré niektorí považujú za intuitívnejšie ako písanie kódu.

2. Syntéza

Po dokončení dizajnu je ďalším krokom syntéza, kde nástroj ako Xilinx XST (XilInx Synthesis Technology) transformuje váš kód HDL alebo schematický dizajn na netlist.Tento netlist popisuje obvod z hľadiska všeobecných digitálnych komponentov, ako sú logické brány a registre.Proces syntézy tiež zahŕňa optimalizáciu návrhu tak, aby spĺňala požiadavky na výkon a minimalizovala využitie zdrojov pre efektívnu prevádzku FPGA.

3. Implementácia

Proces implementácie sa začína prekladom, ktorý kombinuje váš návrh s obmedzenými súbormi, ktoré určujú parametre, ako sú hodinové frekvencie a priradenia PIN.Po preklade fáza mapovania priraďuje prvky vášho netlistu konkrétnym fyzickým zdrojom na FPGA, ako sú vyhľadávacie tabuľky (LUTS) a žabky.Fáza umiestnenia a smerovania potom určuje fyzické umiestnenia každého komponentu v architektúre FPGA a vytvára medzi nimi spojenia prostredníctvom programovateľných zdrojov prepojenia.Táto fáza je vynikajúca na dosiahnutie požadovaných metriiek výkonu vrátane frekvencií hodín.

4. Generovanie bitov

Po úspešnom umiestnení a smerovaní nástroj vygeneruje Bitstream, binárny konfiguračný súbor, ktorý obsahuje všetky programovacie informácie pre FPGA.Často sa odporúča simulovať konečný dizajn po umiestnení, aby sa zabezpečilo, že sa Bitstream bude správať podľa očakávania za podmienok.Tento krok overovania pomáha vyhnúť sa potenciálnym problémom počas skutočnej prevádzky.

5. Konfigurácia

Posledný krok zahŕňa načítanie bitov do FPGA pomocou rôznych konfiguračných metód.Režim slave-seriálu, jednoduchá a nákladovo efektívna voľba, nakonfiguruje FPGA prostredníctvom externého hlavného zariadenia, ktoré odosiela dáta sériovo.V Master-Serial Mode FPGA autonómne číta Bitstream z pripojeného sériového prom.V prípade vysokorýchlostných konfigurácií umožňuje režim výberu MAPP rýchlo načítať údaje do FPGA rýchlo načítať údaje do FPGA.Okrem toho sa režim JTAG používa nielen na programovanie, ale aj na testovanie a ladenie, pričom využíva štandardné rozhranie pre programovanie v systéme a testovanie hraníc scan.

XCV200-6FG456C Výhody

Výkonnosť

Séria Xilinx Virtex, do ktorej patrí XCV200-6FG456C, je optimalizovaná pre vysokorýchlostný výkon a ponúka systémové hodiny až 200 MHz.Vďaka tomu je vhodné pre aplikácie, ktoré si vyžadujú rýchle spracovanie údajov, zabezpečujú účinné zaobchádzanie s komplexnými algoritmami a vysokorýchlostnými operáciami, ako sú telekomunikácie, spracovanie a multimédiá.

Podpora štandardov I/O

Tento FPGA podporuje širokú škálu vstupných/výstupných štandardov vrátane LVTTL, LVCMOS, PCI, GTL, HSTL, SSTL, CTT a AGP.Takáto rozsiahla podpora I/O štandardov umožňuje plynule integráciu s rôznymi komponentmi systému XCV200-6FG456C, čím sa zvýši jeho užitočnosť v rôznych digitálnych ekosystémoch.Táto flexibilita umožňuje prispôsobiť FPGA rôznym podmienkam rozhrania bez modifikácií systému.

Správa

XCV200-6FG456C zahŕňa viacero slučiek s oneskorením (DLL) pre distribúciu a správu hodín v systéme.Tieto DLL pomáhajú pri zlepšovaní načasovania a spoľahlivosti systému poskytovaním presných hodinových signálov potrebné pre synchrónne operácie.Táto vlastnosť je dôležitá pri znižovaní chýb systémov a zvyšovaní celkového výkonu, najmä v zložitých dizajnoch, ktoré si vyžadujú presné načasovanie a synchronizáciu.

Flexibilita dizajnu

S 1 176 konfigurovateľnými logickými blokmi a 5 292 logickými bunkami ponúka XCV200-6FG456C značné logické zdroje so schopnosťou implementovať rozmanitú škálu funkcií.Od jednoduchej logiky lepidla po zložité digitálne systémy tento FPGA podporuje zložité návrhy, čo je ideálna pre aplikácie pri vlastných výpočtoch, spracovaní digitálneho signálu a prototypovania.

Rýchle prototypovanie

FPGA ako XCV200-6FG456C sú známe svojou schopnosťou podporovať rýchle prototypovanie.Toto zariadenie umožňuje rýchle iterácie dizajnu a dá sa rekonfigurovať v poli, čo je výhodou pre vývojové cykly, pretože znižuje čas na trh.Efektívne sa prispôsobuje zmenám požiadaviek alebo aktualizácií v špecifikáciách projektu, čím sa zabezpečuje, že konečné výrobky sú aktuálne s najnovšími technologickými normami.

Integrácia

Integrácia schopností XCV200-6FG456C uľahčuje konsolidáciu viacerých diskrétnych komponentov do jedného čipu.Táto integrácia môže viesť k zníženej zložitosti systému, nižšej spotrebe energie a úsporám nákladov.Minimalizáciou počtu potrebných samostatných komponentov tento FPGA zjednodušuje konštrukčné procesy a zlepšuje spoľahlivosť a kompaktnosť celkového systému.

XCV200-6FG456C Dimenzie obalu

XCV200-6FG456C je terénne programovateľné brána (FPGA) zo série AMD VIRTEX®, umiestneného v balíku 456-loptičiek s jemnou mriežkou (FBGA) (FBGA).

• Typ balíka: 456-FBGA

• Veľkosť: 23 mm x 23 mm

• Výška lopty: 1,0 mm

XCV200-6FG456C Výrobca

XCV200-6FG456C je terénne programovateľné brána (FPGA), ktoré pôvodne vyvinula spoločnosť Xilinx, spoločnosť známa svojimi vysoko výkonnými programovateľnými logickými zariadeniami.Po akvizícii spoločnosti Xilinx by spoločnosťou AMD, XCV200-6FG456C je teraz spojený s AMD ako jeho súčasným výrobcom.Tento model FPGA je však zastaraný a už nie je vo výrobe.AMD naďalej podporuje novšie architektúry FPGA so zvýšenou výkonnosťou, energetickou účinnosťou a rozšírenou životnosťou, vďaka čomu je moderné alternatívy preferované pre nové návrhy.

Záver

XCV200-6FG456C je všestranný a vysokorýchlostný FPGA, ktorý je užitočný pre mnoho technologických aplikácií.Aj keď sa už nevyrába, stále je to dobrá voľba pre staršie systémy, ktoré si vyžadujú spoľahlivý výkon.Táto príručka pokrývala jeho dizajn, programovacie kroky a praktické použitie, čo uľahčuje pochopenie toho, ako funguje a ako sa dá použiť.Keď bude k dispozícii novšie FPGA, môžete použiť tieto znalosti na výber správne FPGA pre vaše potreby a zlepšenie digitálnych návrhov.

Datasheet pdf

XCV200-6FG456C DataShety:

O nás

ALLELCO LIMITED

Čítaj viac

Rýchly dopyt

Zašlite prosím dotaz, okamžite odpovieme.

často kladené otázky [FAQ]

1. Aká je spotreba energie XCV200-6FG456C?

XCV200-6FG456C pracuje pri 2,5 V s rozsahom napätia 2,375 V až 2,625V.Spotreba energie závisí od logického využitia a frekvencie hodín, ale ako staršia FPGA môže byť menej výkonná ako novšie zariadenia Xilinx.Malo by sa brať do úvahy správne riadenie energie a rozptyl tepla.

2. Ako porovnáva XCV200-6FG456C s XCV200-6FG256C?

Model XCV200-6FG456C má väčší balík (456-guľový FBGA) v porovnaní s XCV200-6FG256C (256-loptu FBGA), ktorý ponúka viac I/O pinov (284 vs. 172) a potenciálne lepší výkon pre aplikácie, ktoré si vyžadujú rozsiahle rozhranie.Ak sa váš dizajn spolieha na ďalšie I/O schopnosti, lepšou voľbou je XCV200-6FG456C.

3. Môžem preprogramovať XCV200-6FG456C viackrát?

Áno, XCV200-6FG456C je FPGA založená na SRAM, čo znamená, že sa dá preprogramovať neobmedzený počet, pokiaľ sa dodáva energia.Na udržanie Bitstream po výkonovom cykle však budete potrebovať externú neprchavú pamäť (EEPROM alebo Flash).

4. Podporuje XCV200-6FG456C vysokorýchlostnú sériovú komunikáciu?

XCV200-6FG456C podporuje viacero štandardov I/O, ako sú LVTTL, LVCMOS, PCI, GTL, HSTL a SSTL, ale nemá zabudované vysokorýchlostné SERDE (Serializer/Deserializer) alebo transceivery ako moderné FPGA.V prípade aplikácií vyžadujúcich vysokorýchlostné sériové spojenia (napr. PCIe, Gigabit Ethernet alebo HDMI) zvážte novšie modely FPGA.

5. Ako porovnáva model XCV200-6FG456C s novšími modelmi FPGA?

XCV200-6FG456C patrí do staršej generácie FPGA.V porovnaní s modernými Virtex FPGA má nižší počet brán, pomalšie rýchlosti hodín a obmedzenú výkonovú účinnosť.Novšie modely ponúkajú vyššiu logickú hustotu, viac vloženú pamäť, pokročilé bloky DSP a nižšiu spotrebu energie, čo ich zlepšuje pre moderné aplikácie.

AD73322AR Pinout, Funkcie a technické podrobnosti vysvetlené

na 2025/03/21

EP20K100EFC324-1X FPGA: Funkcie, špecifikácie, aplikácie a programovací sprievodca

na 2025/03/20

Populárne príspevky

-

Komplexné súpravy inštrukcií: Ako zmenili výpočty?

na 8000/04/19 147781

-

USB-C Pinout a funkcie

na 2000/04/19 112056

-

Pomocou Xilinx Unified Simulation Primitive: Komplexný sprievodca dizajnom a simuláciou FPGA

na 1600/04/19 111352

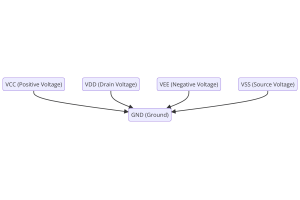

-

Napájacie napätia v elektronike: Význam VCC, VDD, VEE, VSS a GND

na 0400/04/19 83810

-

Sprievodca konektorom RJ45: Pinout, kábly, typy káblov a použitia

na 1970/01/1 79622

-

Konečný sprievodca k farebným kódom drôtu v moderných elektrických systémoch

Spôsob, akým naše elektrické systémy používajú farby, nie je len pre vzhľad.Každá farba drôtu teraz označuje špecifickú funkciu, čo uľahčuje správne identifikáciu a spracovanie elektrických kompone...na 1970/01/1 66994

-

Sprievodca čistením ventilu: funkcia, príznaky, testovanie a výmena za optimálny výkon motora

Čistý ventil je kľúčovou súčasťou systému automobilu, ktorý pomáha udržiavať vzduch čistý riadením výparov paliva skôr, ako môžu uniknúť do atmosféry.To nielen pomáha životnému prostrediu znížením ...na 1970/01/1 63118

-

Kvalita (Q) Faktor: Rovnice a aplikácie

Faktor kvality alebo „Q“ je dôležitý pri kontrole, ako dobre induktory a rezonátory pracujú v elektronických systémoch, ktoré používajú rádiové frekvencie (RF).'Q' meria, ako dobre obvod minimalizu...na 1970/01/1 63057

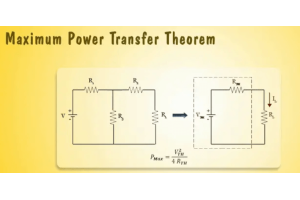

-

Dosiahnutie maximálneho výkonu s maximálnou vetou prenosu energie

Maximálna veta prenosu energie vysvetľuje, ako energia zo zdroja, napríklad batéria alebo generátor, tečie na pripojené zaťaženie.Zobrazuje presnú podmienku, keď zaťaženie prijíma najviac energie.T...na 1970/01/1 54097

-

Špecifikácie batérie A23 a kompatibilita

Batéria A23 je malá batéria v tvare valca s vysokým napätím.Nazýva sa tiež 23A, 23ae alebo MN21, beží na 12 voltoch a oveľa vyšších ako batérie AA alebo AAA.Vďaka jeho špeciálnemu dizajnu ...na 1970/01/1 52207