XC2S50-5TQG144I FPGA: Funkcie, špecifikácie, aplikácie a programovanie

XC2S50-5TQG144I je flexibilný a výkonný FPGA (pole programovateľné poľa GATE) z rodiny Spartan-II spoločnosti AMD Xilinx.Je určený pre digitálne projekty, ktoré si vyžadujú prispôsobenie, rýchlosť a spoľahlivosť.Táto príručka vysvetľuje funkcie, špecifikácie, proces programovania a použitie tohto FPGA, ktoré vám pomôžu pochopiť, ako čo najlepšie využiť.Katalóg

Prehľad XC2S50-5TQG144I

Ten XC2S50-5TQG144i je Spartan-II FPGA od AMD Xilinx, navrhnutý pre digitálne projekty, ktoré si vyžadujú flexibilitu a výkon.Má 50 000 systémových brán a 1 728 logických buniek, čo jej umožňuje zvládnuť zložité úlohy.Čip obsahuje 384 konfigurovateľných logických blokov (CLB) a 32 768 bitov RAM, čo mu dáva dobrú pamäť a spracovateľský výkon.Pri 92 vstupných/výstupných (I/O) kolíkoch sa môže ľahko pripojiť k iným komponentom.Dodáva sa v 144-kolíkovom tenkom štvorkolskom plochom balení (TQFP), ktoré je kompaktné a ľahko použiteľné.FPGA beží na 2,5 V (s bezpečným rozsahom 2,375 V až 2,625 V) a funguje dobre pri teplotách medzi -40 ° C a +100 ° C.Táto FPGA Spartan-II sa vyrába pomocou technológie 0,18-mikrónovej, vďaka čomu je efektívna a spoľahlivá.Je programovateľný, čo znamená, že podľa potreby môžete aktualizovať svoje funkcie.

Pre nákladovo efektívne, vysoko výkonné riešenie je zadržanie hromadnej objednávky s nami optimálnou voľbou, ktorá zaisťuje vynikajúcu kvalitu.

XC2S50-5TQG144I CAD MODELY

Symbol XC2S50-5TQG144i

XC2S50-5TQG144i Footprint

XC2S50-5TQG144I 3D model

XC2S50-5TQG144i Funkcie

• Systémové brány: FPGA XC2S50-5TQG144I ponúka približne 50 000 systémových brán.To jej umožňuje podporovať zložité digitálne návrhy a aplikácie, ktoré si vyžadujú značné množstvo schopností spracovania logiky.

• Logické bunky: Toto zariadenie obsahuje 1 728 logických buniek, ktoré uľahčujú implementáciu zložitých logických konfigurácií a vytváranie rôznych digitálnych funkcií v rámci FPGA.

• Konfigurovateľné logické bloky (CLBS): Je vybavený 384 konfigurovateľnými logickými blokmi (CLB), ktoré poskytujú základ pre logiku FPGA.Tieto bloky môžu byť naprogramované a rekonfigurované tak, aby vyhovovali špecifickým požiadavkám na konštrukciu, čím sa zlepšila celková univerzálnosť zariadenia.

• Búchať: FPGA je vybavená 32 768 bibami interného pamäte RAM, ktoré ponúka efektívne schopnosti ukladania údajov a získavania úloh pre úlohy, ktoré zahŕňajú manipuláciu s údajmi a dočasné ukladanie údajov.

• PIN/O: S 92 pinmi I/O, XC2S50-5TQG144i zaisťuje dostatok externého pripojenia, čo mu umožňuje prepojiť sa s inými zariadeniami a komponentmi v systéme pre komplexnú integráciu systému.

• Prevádzkové napätie: Zariadenie pracuje pri nominálnom napätí 2,5 V, s prijateľným rozsahom od 2,375 V do 2,625 V.Tento rozsah napätia pomáha zabezpečiť stabilnú prevádzku a spoľahlivý výkon za rôznych elektrických podmienok.

• Teplotný rozsah: XC2S50-5TQG144i je navrhnutý tak, aby efektívne fungoval v širokom teplotnom rozsahu, od -40 ° C do +100 ° C, vďaka čomu je vhodný na nasadenie v prostrediach s náročnými tepelnými podmienkami.

XC2S50-5TQG144i Bloková schéma

Diagram ukazuje, ako signály sa pohybujú dovnútra a von z XC2S50-5TQG144I FPGA.Vysvetľuje, ako čip spracováva signály vstupov a výstupov na komunikáciu s inými komponentmi.Na výstupná strana , signály pochádzajú zvnútra FPGA a prechádzajú úložnými jednotkami nazývané žabky.Tieto žabky uchovávajú údaje a uistite sa, že sa signály menia v pravý čas.Signály potom prechádzajú programovateľnou výstupnou vyrovnávacou pamäťou, ktorá upravuje, aký silný je signál, a riadi, ako rýchlo sa mení.K dispozícii je tiež prepínač (ovládací prvok OE), ktorý rozhoduje, či by mal byť výstup aktívny alebo zostať mimo.Ochranný obvod zabraňuje poškodeniu statickej elektriny skôr, ako signál dosiahne vstupno -výstupné kolíky, ktoré sa pripájajú k iným zariadeniam.Na vstupná strana, Signály zvonku vstupujú cez programovateľnú vstupnú vyrovnávaciu pamäť, ktorá ich spracováva pred ich odoslaním do FPGA.Programovateľná jednotka oneskorenia pomáha upravovať načasovanie signálu, takže všetko zostáva synchronizované.FPGA môže tiež použiť interné referenčné napätie (VREF) na zhodné úrovne napätia, čo uľahčuje prácu s rôznymi typmi obvodov.Niektoré kolíky I/O zdieľajú tento odkaz na napätie, aby boli signály stabilné.Tento návrh pomáha FPGA efektívne spravovať signály a zaisťuje správne načasovanie, ochranu a kompatibilitu s rôznymi elektronickými komponentmi.

XC2S50-5TQG144i Špecifikácie

|

Typ |

Parameter |

|

Výrobca |

Amd xilinx |

|

Séria |

Spartan®-II |

|

Balenie |

Podnos |

|

Stav |

Zastaraný |

|

Počet laboratórií/CLB |

384 |

|

Počet logických prvkov/buniek |

1728 |

|

Celkový baranový kúsok |

32 768 |

|

Počet I/O |

92 |

|

Počet brán |

50 000 |

|

Napätie - napájanie |

2,375V ~ 2,625V |

|

Montáž |

Povrchová montáž |

|

Prevádzková teplota |

-40 ° C ~ 100 ° C (TJ) |

|

Balenie |

144-lqfp |

|

Balík dodávateľských zariadení |

144-TQFP (20x20) |

|

Základné číslo produktu |

XC2S50 |

Aplikácie XC2S50-5TQG144i

Zabudované systémy

V zabudovaných systémoch poskytuje XC2S50-5TQG144I potrebnú logiku pre aplikácie založené na mikrokontroléroch.Vo veľkej miere sa používa v automobilovej elektronike, prenosných zariadeniach a robotikách v malom rozsahu na zvýšenie funkčnosti a citlivosti.

Spracovanie signálu

FPGA vyniká v úlohách spracovania signálu, kde je potrebná schopnosť vykonávať paralelné spracovanie.Je ideálny na spracovanie zvuku a videa, telekomunikácie a analýzy údajov, ktorá poskytuje výkon koní na spracovanie zložitých algoritmov a vysokorýchlostných dátových tokov.

Priemyselné riadiace systémy

Systémy priemyselného riadenia majú úžitok z tejto robustnosti a programovateľnosti tejto FPGA, vďaka čomu je vhodný pre aplikácie, ako sú riadenie procesu, automatizácia strojov a monitorovanie systému.Jeho spoľahlivosť zabezpečuje konzistentný výkon v prostrediach, ktoré si vyžadujú presnú a prevádzkovú stabilitu.

Komunikačné systémy

V komunikačných systémoch pomáha XC2S50-5TQG144I spravovať prenos a príjem údajov, podporné činnosti, ako je modulácia signálu a demodulácia, konverzia protokolu a smerovanie siete.Jej adaptabilita je kľúčom k vývoju telekomunikačných infraštruktúr a vznikajúcich bezdrôtových technológií.

Prototypovanie a vývoj

FPGA sa vo veľkej miere používa na prototypovanie digitálnych obvodov.Mnohí ho využívajú na testovanie a vylepšenie svojich nápadov pred konečnou výrobou, najmä v zložitých projektoch dizajnu čipov ASIC a Custom Chip.Táto schopnosť znižuje čas vývoja a náklady a urýchľuje cestu z konceptu na trh.

XC2S50-5TQG144i Podobné časti

XC2S50-5TQG144i Výhody

Nákladová efektívnosť

XC2S50-5TQG144I sa vyznačuje cenovo dostupnosť a dodáva viac funkcií za dolár ako mnoho konkurenčných FPGA.Táto nákladová efektívnosť sa dosahuje prostredníctvom technológie pokročilých procesov a efektívnej architektúry, ktorá umožňuje širšie nasadenie na nákladovo citlivých trhoch.

Vysoko výkonné I/O a balenie

Tento FPGA podporuje širokú škálu I/O štandardov a je k dispozícii v rôznych nákladovo efektívnych možnostiach balenia.Tieto funkcie zabezpečujú, aby zariadenie bolo integrované do viacerých aplikácií bez obetovania výkonu, vďaka čomu je ideálne pre špičkové aj objemové trhy, kde sú všestrannosť rozhrania a fyzické obmedzenia.

Funkcie na úrovni systému

XC2S50-5TQG144I, vybavený funkciami pokročilej správy pamäte, ako je distribuovaná RAM a konfigurovateľná bloková RAM, zvyšuje účinnosť manipulácie s údajmi.Tieto funkcie uľahčujú zložité úlohy ukladania a spracovania údajov, čím sa zvyšuje celkový výkon a škálovateľnosť systému.

Preprogramovateľnosť

Preprogramovateľnosť XC2S50-5TQG144i umožňuje neobmedzené úpravy jeho konfigurácie, čo je prospešné počas vývojovej fázy.Táto flexibilita umožňuje vylepšiť návrhy prostredníctvom iteračných aktualizácií bez ďalších nákladov na hardvér, podpore inovácií a skrátenia času do konečného produktu.

XC2S50-5TQG144I Programovacie kroky

Programovanie FPGA XC2S50-5TQG144 FPGA zo série Spartan-II AMD Xilinx zahŕňa štruktúrovanú sériu krokov určených na efektívne preklad digitálneho dizajnu do funkčnej konfigurácie FPGA.Tu je integrovaný a podrobný sprievodca, ktorý vám pomôže prostredníctvom procesu programovania:

1. Návrh

Začnite s fázou vstupu dizajnu, kde vytvárate svoju digitálnu logiku pomocou jazyka Hardware Popis (HDL), ako je VHDL alebo Verilog.Tento počiatočný krok zahŕňa podrobnosti o funkciách a logike, ktorú chcete implementovať v FPGA.Vyžaduje sa, aby bol váš dizajn presný a presne predstavuje zamýšľané operácie na zabezpečenie úspešnej syntézy a implementácie.

2. Syntéza

V kroku syntézy využite syntézu nástroja na prevedenie kódu HDL na netlist.NetList je rozdelením vášho dizajnu do formátu, ktorý obsahuje rôzne vzájomne prepojené logické prvky, ako sú brány a žabky.Tento proces prekladá váš teoretický dizajn do praktického plánu, ktorému FPGA môže porozumieť a implementovať.

3. Implementácia

Implementácia zahŕňa niekoľko čiastkových krokov: mapovanie, umiestnenie a smerovanie.Mapovanie priraďuje prvky vášho netlistu do konkrétnych logických blokov v rámci FPGA.Umiestnenie fyzických umiestnení týchto blokov na čip FPGA na optimalizáciu výkonu a využitia zdrojov.Routing spája tieto bloky prostredníctvom programovateľných vzájomných zdrojov FPGA.Táto fáza zaisťuje, že dizajn spĺňa všetky fyzické a výkonné obmedzenia.

4. Definícia obmedzenia

Počas procesu navrhovania je potrebné definujúce obmedzenia.Obmedzenia usmerňujú implementačné nástroje určením požiadaviek, ako je načasovanie (ako rýchlo by mal FPGA fungovať), a priradenia PIN (ktoré kolíky na FPGA sa pripoja k rôznym častiam vášho hardvéru).Sú kĺbené v súbore používateľských obmedzení (UCF), ktorý pomáha pri doladení návrhu, aby spĺňal konkrétne prevádzkové normy.

5. Generovanie bitov

Akonáhle váš dizajn úspešne prejde fázou implementácie, ďalším krokom je vygenerovanie súboru Bitstream.Tento súbor obsahuje všetky konfiguračné údaje, ktoré FPGA potrebuje na vykonanie návrhu.Bitstream je konečný výstup procesu programovania, ktorý predstavuje kompletný programovaný stav FPGA.

6. Programovanie zariadení

Posledným krokom je načítať Bitstream do fpGA XC2S50-5TQG144i, ktorý je možné vykonať pomocou rôznych konfiguračných režimov v závislosti od vášho nastavenia.V Hlavný sériový režim, FPGA autonómne číta konfiguračné údaje z pripojeného sériového prom (programovateľná pamäť iba na čítanie). Otrokársky režim Umožňuje externé hlavné zariadenie, ako je napríklad mikrokontrolér, sériovo napájanie konfiguračných údajov FPGA. Paralelný režim Umožňuje vysokorýchlostné programovanie poskytovaním konfiguračných údajov paralelne z externého hlavného zariadenia.Nakoniec, Režim hraničného skenovania (JTAG) Využíva rozhranie JTAG pre programovanie aj testovanie, vďaka čomu je užitočné počas vývoja pre iteračné ladenie a overovanie.

XC2S50-5TQG144i Dimenzie obalu

Ten XC2S50-5TQG144i je terénne programovateľné brána (FPGA) z rodiny Spartan-II v rodine Xilinx, umiestneného v a Balíček s tenkým štvorkolkou na tenké štvorkolky (TQFP).Tento balík meria 20 mm x 20 mm.

XC2S50-5TQG144I Výrobca

XC2S50-5TQG144i je FPGA z rodiny Spartan-II, ktorú vyrobil AMD Xilinx.Xilinx, teraz súčasť AMD, je popredná polovodičová spoločnosť špecializujúca sa na FPGA, adaptívne SOC a ďalšie programovateľné logické zariadenia.XC2S50-5TQG144i bol pôvodne vyvinutý v sérii Xilinx Spartan-II, ktorý ponúka 50 000 systémových brán a 1 728 logických buniek určených pre vysoko výkonné, ale nákladovo efektívne aplikácie.Vďaka akvizícii spoločnosti Xilinx spoločnosťou AMD spoločnosť naďalej podporuje staršie produkty, ako je séria Spartan-II, pričom rozvíja novšie architektúry FPGA.XC2S50-5TQG144i je však FPGA staršej generácie a môže čeliť prípadnému zastarávaniu, pretože AMD Xilinx sa zameriava na pokročilejšie rodiny FPGA.

Záver

FPGA XC2S50-5TQG144I je nákladovo efektívny a preprogramovateľný čip, ktorý ponúka skvelý výkon a flexibilitu.Všeobecne sa používa v zabudovaných systémoch, priemyselných strojoch a komunikačných sieťach kvôli svojmu vysokorýchlostnému spracovaniu a silným možnostiam pripojenia.Vďaka svojej schopnosti byť naprogramovaním a aktualizáciou tento FPGA pomáha pred konečnou výrobou testovať a rozvíjať nové nápady.Aj keď sú k dispozícii novšie FPGA, tento model zostáva solídnou voľbou pre projekty, ktoré potrebujú spoľahlivé a cenovo dostupné riešenie FPGA.Táto príručka poskytuje jasný a jednoduchý prehľad funkcií, použití a programovania FPGA, čo z neho robí cenný zdroj pre všetkých.

O nás

ALLELCO LIMITED

Čítaj viac

Rýchly dopyt

Zašlite prosím dotaz, okamžite odpovieme.

často kladené otázky [FAQ]

1. Môžem použiť XC2S50-5TQG144i pre vysokorýchlostné aplikácie?

XC2S50-5TQG144I podporuje rýchlosti až 200 MHz, vďaka čomu je vhodná pre väčšinu zabudovaných a priemyselných aplikácií.Ak však váš projekt vyžaduje vysokorýchlostné rozhrania, ako je PCIe alebo DDR pamäť, možno budete potrebovať pokročilejší FPGA, ako je séria Spartan-6 alebo Artix-7.

2. Ako porovnáva XC2S50-5TQG144i s novšími spartan-3 alebo spartan-6 FPGA?

Zatiaľ čo novšie FPGA ako Spartan-3 alebo Spartan-6 ponúkajú zvýšený výkon, vyššiu hustotu logiky a ďalšie funkcie, XC2S50-5TQG144i zostáva preferovanou voľbou pre nákladovo citlivé projekty so miernou zložitosťou.Ak potrebujete starú kompatibilitu alebo stabilný dodávateľský reťazec, je skvelá voľba XC2S50-5TQG144i.

3. Aké programovacie nástroje sú kompatibilné s FPGA XC2S50-5TQG144I?

XC2S50-5TQG144i je naprogramovaný pomocou Xilinx ISE (Integrované softvérové prostredie).Zatiaľ čo novšie nástroje Xilinx, ako je Vivado, nepodporujú rodinu Spartan-II, ISE poskytuje pre tento FPGA všetky potrebné dizajn, syntézu a programovacie funkcie.

4. Môžem migrovať existujúci dizajn Spartan-II na novší FPGA?

Áno, ale vyžaduje to úpravy.Novšie rodiny Spartan-3 a Spartan-6 používajú rôzne architektúru, úrovne napätia a konfiguračné metódy.Ak uvažujete o migrácii, môžeme pomôcť pri výbere vhodných alternatív a minimalizácii zmien dizajnu.

5. Podporuje XC2S50-5TQG144i programovanie JTAG?

Odpoveď: Áno, FPGA podporuje programovanie hraničného skenovania JTAG (IEEE 1149.1), ktoré umožňuje ľahké ladenie a konfiguráciu pomocou štandardného rozhrania JTAG.Je to užitočné pre počiatočné programovanie a rekonfiguráciu bez externej pamäte.

XC4013XL-3PQ240C FPGA: Alternatívy, špecifikácie, aplikácie a datasheet

na 2025/03/18

Zosilňovače RF Power: Ako fungujú, ktorý typ je efektívnejší

na 2025/03/18

Populárne príspevky

-

Komplexné súpravy inštrukcií: Ako zmenili výpočty?

na 8000/04/18 147761

-

USB-C Pinout a funkcie

na 2000/04/18 111982

-

Pomocou Xilinx Unified Simulation Primitive: Komplexný sprievodca dizajnom a simuláciou FPGA

na 1600/04/18 111351

-

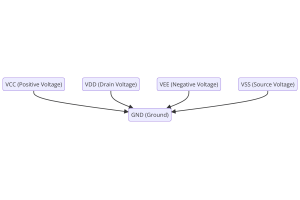

Napájacie napätia v elektronike: Význam VCC, VDD, VEE, VSS a GND

na 0400/04/18 83743

-

Sprievodca konektorom RJ45: Pinout, kábly, typy káblov a použitia

na 1970/01/1 79534

-

Konečný sprievodca k farebným kódom drôtu v moderných elektrických systémoch

Spôsob, akým naše elektrické systémy používajú farby, nie je len pre vzhľad.Každá farba drôtu teraz označuje špecifickú funkciu, čo uľahčuje správne identifikáciu a spracovanie elektrických kompone...na 1970/01/1 66944

-

Sprievodca čistením ventilu: funkcia, príznaky, testovanie a výmena za optimálny výkon motora

Čistý ventil je kľúčovou súčasťou systému automobilu, ktorý pomáha udržiavať vzduch čistý riadením výparov paliva skôr, ako môžu uniknúť do atmosféry.To nielen pomáha životnému prostrediu znížením ...na 1970/01/1 63086

-

Kvalita (Q) Faktor: Rovnice a aplikácie

Faktor kvality alebo „Q“ je dôležitý pri kontrole, ako dobre induktory a rezonátory pracujú v elektronických systémoch, ktoré používajú rádiové frekvencie (RF).'Q' meria, ako dobre obvod minimalizu...na 1970/01/1 63026

-

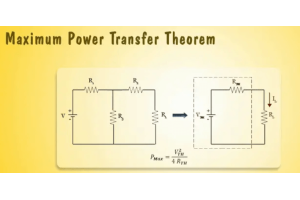

Dosiahnutie maximálneho výkonu s maximálnou vetou prenosu energie

Maximálna veta prenosu energie vysvetľuje, ako energia zo zdroja, napríklad batéria alebo generátor, tečie na pripojené zaťaženie.Zobrazuje presnú podmienku, keď zaťaženie prijíma najviac energie.T...na 1970/01/1 54092

-

Špecifikácie batérie A23 a kompatibilita

Batéria A23 je malá batéria v tvare valca s vysokým napätím.Nazýva sa tiež 23A, 23ae alebo MN21, beží na 12 voltoch a oveľa vyšších ako batérie AA alebo AAA.Vďaka jeho špeciálnemu dizajnu ...na 1970/01/1 52167