LFEC3E-3Q208C Prehľad FPGA: Funkcie, aplikácie, programovanie a špecifikácie

V tomto článku sa dozviete viac o LFEC3E-3Q208C, FPGA z Lattice Semiconductor.Uvidíte, čo to je, hlavné funkcie, ktoré ponúka, a prečo je užitočný pre mnoho dizajnov stredného rozsahu.Obsah vás tiež prevedie svojimi špecifikáciami, aplikáciami a procesom programovania krok za krokom, spolu s jeho výhodami, nevýhodami a podrobnosťami výrobcu.Katalóg

Čo je LFEC3E-3Q208C?

Ten LFEC3E-3Q208C je nákladovo efektívny terénny programový program Gate Array (FPGA) z Semiconductor Mretice, navrhnutý ako súčasť rodiny Latticeec (Economic).Táto rodina bola vyvinutá s cieľom poskytovať programovateľné logické riešenia, ktoré vyvážia cenovú dostupnosť so spoľahlivým výkonom pre bežné návrhy.V rámci hierarchie Latticeec sa nachádza v strednom rozsahu a ponúka okolo 3 000 logických prvkov a efektívne využitie energie, ktoré preklenujú medzeru medzi menšími vstupnými zariadeniami a väčšími a viac náročnými modelmi.Širšia séria Latticeecp/EC zdôrazňuje lacnú programovateľnosť, škálovateľnosť a flexibilitu vo viacerých veľkostiach zariadení, pričom variant EC sa zameriava na výkon založený na ekonomike.

Hľadáte LFEC3E-3Q208C?Kontaktujte nás a skontrolujte aktuálne zásoby, dodací čas a ceny.

Funkcie LFEC3E-3Q208C

• Logické zdroje

Zariadenie integruje približne 3 100 logických prvkov usporiadaných do 384 blokov, čím mu poskytuje dostatočnú kapacitu pre návrhy stredného rozsahu.Vďaka tejto rovnováhe zdrojov je vhodná pre riadiacu logiku, spracovanie signálu a vložené aplikácie bez nadmerných nákladov.

• Programovateľné I/O

S až 145 programovateľnými vstupnými/výstupnými kolíkmi podporuje širokú škálu možností pripojenia.Tieto I/OS sú kompatibilné s viacerými normami, ako sú LVCMOS, LVTTL, LVDS, PCI a SSTL, čo umožňuje flexibilnú integráciu systému.

• Vložená pamäť

FPGA obsahuje vyhradený blok RAM (EBR) a distribuované zdroje RAM, ktoré poskytujú efektívne úložisko na čipe.To umožňuje implementovať vyrovnávanie údajov, vyhľadávacie tabuľky alebo malé zabudované spomienky priamo vo vnútri zariadenia.

• Správa

Ponúka až štyri integrované PLL, ktoré ponúka frekvenčné násobenie, delenie a posun fázy.To umožňuje presné riadenie načasovania a synchronizáciu vysokorýchlostných návrhov.

• Podpora pamäte DDR

Zariadenie obsahuje hardvérovú podporu pre rozhrania DDR, schopné spustiť DDR400 (200 MHz).Vďaka tomu je praktické pre vzory, ktoré si vyžadujú externý vysokorýchlostný prístup pamäte.

• Výkonnosť

FPGA, ktorá pracuje s jadrom 1,2 V, minimalizuje celkovú spotrebu energie systému.Jeho nízkoenergetický dizajn je ideálny pre prenosné alebo energeticky citlivé aplikácie.

• Funkcie na úrovni systému

Vstavané funkcie, ako napríklad IEEE 1149.1 hraničné skenovanie, logická analýza na čipoch (ISPTRACY) a rozhranie SpI Boot Flash, zjednodušujú testovanie a ladenie.Tieto funkcie znižujú čas vývoja a zlepšujú spoľahlivosť dizajnu.

• Rozvoj

Podporené spoločnosťou Isplever Design Suite, zariadenie ťaží z automatizovanej syntézy, miesta a smerov a overovacích nástrojov.Môžete tiež použiť ISpleverCore IP bloky na urýchlenie bežných funkcií a skrátenie času na trh.

Schéma blokového bloku Latticeecp/EC

Bloková schéma rodiny Latticeecp/EC (vrátane LFEC3E-3Q208C) ukazuje, ako je FPGA zostavená a ako jeho časti spolupracujú.Programovateľné I/O bunky (obrázky) sú umiestnené okolo okrajov na spojenie čipu s vonkajšími zariadeniami, ktoré podporujú mnoho signálnych štandardov.Vo vnútri programovateľné funkčné jednotky (PFUS) manipulujú s logickými operáciami, pričom niektoré spárované až vložené blokové bloky RAM (EBR) na ukladanie údajov a iné zamerané iba na logiku.SysClock PLLS spravujú signály hodín, aby dizajn mohol bežať správnou rýchlosťou a načasovaním.Port SysConfig a port JTAG vám umožňujú ľahko programovať, testovať a ladiť FPGA.Toto usporiadanie poskytuje flexibilitu LFEC3E-3Q208C, spoľahlivý výkon a jednoduchú integráciu do nákladovo citlivých návrhov.

Schéma Schéma Latticeecp/EC

Plátok v rodine Latticeecp/EC, podobne ako v LFEC3E-3Q208C, je základnou logickou jednotkou, ktorá kombinuje bloky LUT4 a prenášajú bloky na vykonávanie logických a aritmetických operácií.Každý plátok tiež obsahuje žabky/západky na ukladanie údajov a povolenie sekvenčnej logiky, pričom multiplexory na flexibilne smerujú signály buď prostredníctvom registrov alebo priamo.Táto štruktúra je dôležitá, pretože poskytuje rýchlosť, flexibilitu a efektívnosť FPGA na zvládnutie jednoduchých aj zložitých digitálnych návrhov.Nasledujúca tabuľka sumarizuje popisy signálu rezu vrátane ich funkcií, typov, názvov signálov a účelov.

|

Funkcia |

Typ |

Názvy signálov |

Opis |

|

Vstup |

Dátový signál |

A0, B0, C0, D0 |

Vstupy do lut4 |

|

Vstup |

Dátový signál |

A1, B1, C1, D1 |

Vstupy do lut4 |

|

Vstup |

Viacúčelový |

M0 |

Viacúčelový vstup |

|

Vstup |

Viacúčelový |

M1 |

Viacúčelový vstup |

|

Vstup |

Ovládací signál |

CEA |

Umožniť hodinami |

|

Vstup |

Ovládací signál |

LSR |

Miestna sada/reset |

|

Vstup |

Ovládací signál |

Clk |

Systémové hodiny |

|

Vstup |

Signál inter-PFU |

Fcin |

Rýchle prenášanie dovnútra |

|

Výstup |

Dátové signály |

F0, F1 |

Signály obtoku výstupu LUT4 |

|

Výstup |

Dátové signály |

Q0, Q1 |

Zaregistrovať |

|

Výstup |

Dátové signály |

X0 |

Výstup lut5 mux |

|

Výstup |

Dátové signály |

X1 |

Výstup Lut6, lut7, lut8 2 mux v závislosti od plátku |

|

Výstup |

Signál inter-PFU |

Fco |

Pre pravú väčšinu PFU výstup rýchle prepravy¹ |

Špecifikácie LFEC3E-3Q208C

|

Typ |

Parameter |

|

Výrobca |

Mriežkový polovodič |

|

Napätie - napájanie |

1,14V ~ 1,26V |

|

Celkový baranový kúsok |

56 320 |

|

Balík dodávateľských zariadení |

208-PQFP (28x28) |

|

Séria |

ES |

|

Balenie |

208-bfqfp |

|

Balík |

Podnos |

|

Prevádzková teplota |

0 ° C ~ 85 ° C (TJ) |

|

Počet logických prvkov/buniek |

3 100 |

|

Počet I/O |

145 |

|

Montáž |

Povrchová montáž |

|

Základné číslo produktu |

Lfec3 |

LFEC3E-3Q208C Aplikácie

1. Vstavané riadiace systémy

LFEC3E-3Q208C je vhodná pre zabudované ovládače v zariadeniach, priemyselnej automatizácii a bránach IoT.Jeho mierna logická hustota a nízkonákladový dizajn umožňujú nahradiť logiku s pevnou funkciou programovateľnou flexibilitou.To uľahčuje aktualizáciu systémov alebo prispôsobenie sa vyvíjajúcim sa normám bez prepracovania hardvéru.

2. Rozhranie pamäte DDR

S vstavanou podporou pre pamäť DDR400 môže zariadenie spravovať vyrovnávanie údajov, protokolovanie alebo dočasné úložisko v aplikáciách.Táto funkcia je užitočná v systémoch, v ktorých je dôležitá rýchlosť externej pamäte, ale nevyžaduje sa úplný výkon FPGA.Mnohé z nich majú úžitok z rovnováhy rýchlosti, nákladov a efektívnosti pamäte.

3. I/O premosťovanie a konverzia protokolu

Vďaka svojej širokej podpore I/O štandardov ako LVCMOS, LVTTL, LVDS, PCI a SSTL je FPGA účinný pri preklenutí rôznych digitálnych rozhraní.Môže byť nakonfigurovaný tak, aby prekladal signály medzi subsystémami, vďaka čomu je hodnotný v návrhoch zmiešanej technológie.Táto flexibilita pomáha predĺžiť životnosť existujúceho hardvéru tým, že umožňuje kompatibilitu s novými komponentmi.

4. Priemyselné a infraštruktúrne aplikácie

Zariadenie môže slúžiť aj v nákladovo citlivých priemyselných a infraštruktúrnych zariadeniach, kde je dostatočná spoľahlivosť a mierny výkon.Jeho podpora pre hraničné skenovanie, ladenie na čipoch a prevádzka nízkej energie je ideálna pre systémy, ktoré si vyžadujú účinnosť a ľahkú údržbu.Typické úlohy zahŕňajú riadiace jednotky, moduly rozhrania a monitorovacie systémy.

LFEC3E-3Q208C Podobné časti

|

Špecifikácia |

LFEC3E-3Q208C |

LFEC3E-3Q208i |

LFEC3E-3QN208C |

LFEC3E-4Q208C |

LFEC1E-3Q208C

|

LFEC6E-3Q208C

|

|

Logické prvky (LUTS) |

~ 3,1k |

~ 3,1k |

~ 3,1k |

~ 3,1k |

~ 1,5K |

~ 6.1k |

|

Logické bloky |

384 |

384 |

384 |

384 |

192 |

768 |

|

Vstavaný blok RAM (EBR) |

~ 55 kb |

~ 55 kb |

~ 55 kb |

~ 55 kb |

~ 18 kb |

~ 92 kb |

|

Maximálna prevádzková frekvencia |

~ 340 MHz |

~ 340 MHz |

~ 340 MHz |

~ 340 MHz |

~ 300 MHz |

~ 340 MHz |

|

I/O |

145 |

145 |

145 |

145 |

112 |

145 |

|

Balík |

208-pqfp |

208-pqfp |

208-pqfp |

208-pqfp |

208-pqfp |

208-pqfp |

|

Napätie jadra |

1,2 V |

1,2 V |

1,2 V |

1,2 V |

1,2 V |

1,2 V |

|

Teplotný rozsah |

0 ° C až +70 ° C |

–40 ° C až +85 ° C |

0 ° C až +70 ° C |

0 ° C až +70 ° C |

0 ° C až +70 ° C |

0 ° C až +70 ° C |

|

Súlad / typ balíka |

Norma |

Priemyselný |

Bez olova (QN) |

Variant (q) |

Norma |

Norma |

|

Aplikácia |

Stredná hustota, všeobecná správa |

Rovnaké ako LFEC3E, ale priemyselné použitie |

Rovnaké ako LFEC3E, ale sú kompatibilné s balíkom |

Rovnaká rodina, ľahká migrácia |

Možnosť nákladov s nízkou hustotou |

Upgrade s vyššou hustotou |

LFEC3E-3Q208C Programovacie kroky

Predtým, ako začnete programovať LFEC3E-3Q208C, je dôležité pripraviť správne nástroje a porozumieť toku návrhu na konfiguráciu zariadenia.Každý krok vychádza z predchádzajúceho, takže starostlivá pozornosť zabezpečí plynulý proces programovania.

1. Pripravte programovací hardvér a softvér

Začnete inštaláciou diamantového programátora spoločnosti Lattice alebo systém ISPVM, ktoré sú oficiálnymi nástrojmi pre tento FPGA.Potom nastavte programovací kábel JTAG, ako je napríklad HW-USBN-2B, a uistite sa, že sú ovládače správne nainštalované.Tento krok zaisťuje, že váš počítač je pripravený komunikovať s cieľovým zariadením bez chýb pripojenia.

2. Implementujte svoj návrh vo vývojovom softvéri

Ďalej vytvorte nový projekt v Diamantovi mriežky a vyberte ako cieľové zariadenie LFEC3E-3Q208C.Potom pridáte svoje zdrojové súbory Verilog alebo VHDL, použite priradenia PIN a definujete akékoľvek obmedzenia načasovania.Akonáhle sa to stane, syntetizujete dizajn, vykonajte miesto a smerovanie a nakoniec vygenerujete súbor Bitstream (.bit alebo .Jed), ktorý sa použije na programovanie.

3. Nastavte dosku a pripojenia

Pred pripevnením signálnych vedení pripojte kábel JTAG k doske FPGA a pred pripevnením signálnych vedení je zaistený.Potvrďte, že rezistory vytiahnutia a rozťahovania sú správne na svojom mieste, najmä na linkách TCK a otvorených odtokov.Ak má vaša doska ďalšie ovládacie kolíky, ako je vymazanie alebo ISPEN, musíte ich správne nakonfigurovať, aby ste zabránili náhodným resetom počas programovania.

4. Naprogramujte zariadenie

Pri pripravenom hardvéri spustite programovací nástroj a vyberte pripojený kábel.Načítajte vygenerovaný súbor Bitstream a vyberte príslušný režim, zvyčajne JTAG, v závislosti od vášho nastavenia.Spustite proces programovania a nástroj nakonfiguruje FPGA a zároveň overuje, či boli údaje správne napísané.

5. Overte a ladite konfiguráciu

Po programovaní skontrolujte špendlíky Hotovo alebo init na svojej doske, aby ste potvrdili, že FPGA úspešne nakonfigurovala.Ak je to potrebné, použite logický analyzátor ISPTRACE alebo funkcie hraničného skenovania na testovanie funkčnosti a overenie správania signálu.Môžete zopakovať cyklus návrhu a programovania vždy, keď sú potrebné zmeny, a zaistiť, aby bol váš projekt vylepšený krok za krokom.

LFEC3E-3Q208C Výhody a nevýhody

Výhody

• Nízka spotreba energie, vhodná pre energeticky citlivé návrhy

• nákladovo efektívne v porovnaní s vyššími koncovými FPGA

• Jednoduchý nástroj na nástroj s ľahšou krivkou učenia

• Pole Reconfigurovateľný pre aktualizácie po nasadení

• Kompaktný balík s dobrou rovnováhou zdrojov

Nevýhody

• Obmedzený výkon v porovnaní s väčšími FPGA

• Nižšia logika a kapacita pamäte ako zariadenia špičkových

• Menšie IP jadrá tretích strán a podpora ekosystémov

• Toolchain nemá pokročilé funkcie hlavných dodávateľov

• Nie je vhodné pre rozhrania s ultra vysokou rýchlosťou

LFEC3E-3Q208C Dimenzie obalu

|

Typ |

Parameter |

|

Typ balíka |

208-PQFP (Plast Quad Flat Balíček) |

|

Veľkosť tela |

28 mm × 28 mm |

|

Pitch |

0,5 mm |

|

Výška balíka (max) |

~ 3,4 mm |

|

Počet olovu |

208 kolíkov |

|

Štýl |

Vodiče z línií (štvorkoliek) |

|

Montáž |

Povrchová montáž |

|

Kódex |

BFQFP-208 |

|

Dodávateľ |

Podnos |

LFEC3E-3Q208C Výrobca

LFEC3E-3Q208C sa vyrába Mrežová polovodičová spoločnosť , spoločnosť so sídlom v USA so sídlom v Hillsboro v Oregone.Spoločnosť Lattice, ktorá bola založená v roku 1983, sa špecializuje na vývoj nízkoenergetických, nákladovo efektívnych polí programov v teréne (FPGA) a súvisiacich riešení.Spoločnosť sa zameriava na povolenie aplikácií v oblasti komunikácií, výpočtových, spotrebiteľských elektronických, priemyselných a automobilových trhov.Spoločnosť Lattice, ktorá je známa svojou inováciou v oblasti energeticky efektívnych programovateľných zariadení, sa etablovala ako kľúčový hráč v priemysle FPGA, najmä pre návrhy, ktoré vyžadujú faktory kompaktných foriem, zníženú spotrebu energie a vysokú spoľahlivosť.

Záver

LFEC3E-3Q208C ponúka dobrú kombináciu nízkych nákladov, nízkej spotreby a dostatočnú logiku a pamäť pre projekty stredného rozsahu.Podporuje mnoho I/O štandardov, má vstavané RAM a PLLS a môže pracovať s pamäťou DDR400, vďaka čomu je užitočná pre riadenie, rozhranie a priemyselné úlohy.Programovanie je jednoduché s nástrojmi mriežky a ďalšie ladiace funkcie pomáhajú pri testovaní.Aj keď nemôže zodpovedať rýchlosti a kapacite väčších FPGA, je to spoľahlivá voľba pre návrhy, ktoré si vyžadujú flexibilitu, efektívnosť a cenovo dostupný výkon.

Datasheet pdf

LFEC3E-3Q208C DataShety:

O nás

ALLELCO LIMITED

Čítaj viac

Rýchly dopyt

Zašlite prosím dotaz, okamžite odpovieme.

často kladené otázky [FAQ]

1. Podporuje LFEC3E-3Q208C vysokorýchlostné rozhrania, ako sú PCIe alebo Gigabit Ethernet?

Č. LFEC3E-3Q208C je navrhnutý pre aplikácie bežné a nákladovo citlivé, takže nezahŕňa natívne vysokorýchlostné sériové vysielače.Namiesto toho sa zameriava na paralelné rozhrania a podporu pamäte DDR.

2. Dá sa LFEC3E-3Q208C po nasadení preprogramovať?

Áno.Ako FPGA je LFEC3E-3Q208C plne rekonfigurovateľná, čo umožňuje aktualizácie a úpravy navrhovania aj po nasadení.Táto flexibilita znižuje dlhodobé náklady na údržbu a rozširuje životné cykly produktu.

3. Ako zvládne LFEC3E-3Q208C ladenie a testovanie?

Zariadenie integruje hraničné skenovanie (IEEE 1149.1), logickú analýzu na čipoch (ISPTRACY) a podporu SPI Boot Flash.Tieto vstavané nástroje zjednodušujú ladenie a znižujú potrebu externého testovacieho hardvéru.

4. Môže LFEC3E-3Q208C predĺžiť životnosť starších hardvérových systémov?

Áno, vďaka svojej širokej kompatibilite I/O kompatibility a premostenia protokolu môže prepojiť staršie systémy s novšími komponentmi a pomôcť podnikom rozšíriť užitočnosť existujúceho hardvéru.

5. Aké programovacie nástroje sú potrebné pre LFEC3E-3Q208C?

Je naprogramovaný pomocou diamantového programátora spoločnosti Lattice alebo systém ISPVM.Tieto nástroje podporujú zadávanie dizajnu, generovanie bitov a konfiguráciu zariadení, vďaka čomu je pracovný tok zefektívnený.

AD73311Lars: Datashet, funkcie, sprievodca Pinout a programovanie

na 2025/08/28

EPM1270F256C4N Max II Prehľad CPLD: Funkcie, špecifikácie a aplikácie

na 2025/08/28

Populárne príspevky

-

Komplexné súpravy inštrukcií: Ako zmenili výpočty?

na 8000/04/19 147782

-

USB-C Pinout a funkcie

na 2000/04/19 112070

-

Pomocou Xilinx Unified Simulation Primitive: Komplexný sprievodca dizajnom a simuláciou FPGA

na 1600/04/19 111352

-

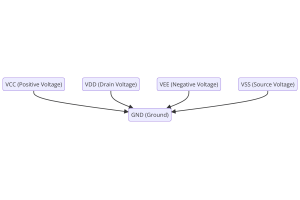

Napájacie napätia v elektronike: Význam VCC, VDD, VEE, VSS a GND

na 0400/04/19 83829

-

Sprievodca konektorom RJ45: Pinout, kábly, typy káblov a použitia

na 1970/01/1 79642

-

Konečný sprievodca k farebným kódom drôtu v moderných elektrických systémoch

Spôsob, akým naše elektrické systémy používajú farby, nie je len pre vzhľad.Každá farba drôtu teraz označuje špecifickú funkciu, čo uľahčuje správne identifikáciu a spracovanie elektrických kompone...na 1970/01/1 67006

-

Sprievodca čistením ventilu: funkcia, príznaky, testovanie a výmena za optimálny výkon motora

Čistý ventil je kľúčovou súčasťou systému automobilu, ktorý pomáha udržiavať vzduch čistý riadením výparov paliva skôr, ako môžu uniknúť do atmosféry.To nielen pomáha životnému prostrediu znížením ...na 1970/01/1 63131

-

Kvalita (Q) Faktor: Rovnice a aplikácie

Faktor kvality alebo „Q“ je dôležitý pri kontrole, ako dobre induktory a rezonátory pracujú v elektronických systémoch, ktoré používajú rádiové frekvencie (RF).'Q' meria, ako dobre obvod minimalizu...na 1970/01/1 63067

-

Dosiahnutie maximálneho výkonu s maximálnou vetou prenosu energie

Maximálna veta prenosu energie vysvetľuje, ako energia zo zdroja, napríklad batéria alebo generátor, tečie na pripojené zaťaženie.Zobrazuje presnú podmienku, keď zaťaženie prijíma najviac energie.T...na 1970/01/1 54097

-

Špecifikácie batérie A23 a kompatibilita

Batéria A23 je malá batéria v tvare valca s vysokým napätím.Nazýva sa tiež 23A, 23ae alebo MN21, beží na 12 voltoch a oveľa vyšších ako batérie AA alebo AAA.Vďaka jeho špeciálnemu dizajnu ...na 1970/01/1 52226