EPM7064STC100-7 CPLD: Funkcie, aplikácie a sprievodca programovaním v systéme

EPM7064STC100-7 je výkonný čip zo série Intel MAX® 7000S, ktorý je navrhnutý na spracovanie zložitých úloh v elektronických zariadeniach.Táto príručka pojednáva o hlavných vlastnostiach a použití EPM7064STC100-7, zdôrazňuje jej schopnosť ľahko preprogramovať, svoju rýchlu prevádzku a flexibilný dizajn.Tento čip je ideálny pre mnoho rôznych technológií, od malých gadgetov po veľké priemyselné stroje, je kľúčovým kusom na budovanie pokročilých digitálnych obvodov.Katalóg

EPM7064STC100-7 Opis

Ten EPM7064STC100-7 je komplexné programovateľné logické zariadenie (CPLD) zo série Intel MAX® 7000S.Má 64 makrocellov a 1 250 brán, ktoré pomáhajú pri budovaní zložitých digitálnych obvodov.Tento čip beží maximálnou rýchlosťou 166,7 MHz, s oneskorením signálu 7,5 nanosekundov (NS).Má 68 vstupných/výstupných (I/O) pinov, ktoré pracujú s logikou 3,3 V a 5 V, čo uľahčuje použitie v rôznych obvodoch.Kľúčovou vlastnosťou je jej 5.0V programovateľnosť systému (ISP) prostredníctvom rozhrania JTAG (IEEE 1149.1).To znamená, že ho môžete preprogramovať bez toho, aby ste ho odstránili z obvodu, čo uľahčuje testovanie a aktualizácie.Dodáva sa v 100-kolíkovom tenkom štvorkolskom plochom balení (TQFP), ktoré je kompaktným balíčkom s povrchovou strechou.Tento CPLD sa používa v zabudovaných systémoch, spracovaní digitálneho signálu, komunikačných zariadení a priemyselnej automatizácii.

Poskytujeme vysoko kvalitné komponenty a prispôsobené služby, takže je najlepšie zadať svoju hromadnú objednávku s nami pre spoľahlivé riešenia CPLD.

Funkcie EPM7064STC100-7

• Logika s vysokou hustotou: EPM7064STC100-7 je navrhnutý so 64 makrocellmi a 1 250 použiteľnými bránami, vďaka čomu je vysoko vhodný na implementáciu zložitých logických funkcií v digitálnych obvodoch.Táto architektúra s vysokou hustotou umožňuje vytvárať zložité logické návrhy pri zachovaní efektívnosti v programovateľných logických operáciách.Dobre optimalizovaná štruktúra makrocelkov zaisťuje efektívne využitie dostupných zdrojov, ktoré podporuje pokročilé kombinované a postupné implementácie logiky.

• Rýchly výkon: EPM7064STC100-7, postavený na vysokorýchlostné spracovanie, pracuje s maximálnou vnútornou frekvenciou 166,7 MHz, čo umožňuje rýchle vykonávanie logických funkcií.Jeho oneskorenie šírenia 7,5 ns zaisťuje minimálnu latenciu.Táto rýchla prepínajúca schopnosť zvyšuje schopnosť zariadenia efektívne zvládnuť vysokorýchlostné spracovanie údajov, kondicionovanie signálu a riadenie, čo z neho robí spoľahlivú voľbu pre náročné digitálne systémy.

• Všestranné I/O: S 68 programovateľnými vstupnými/výstupnými kolíkmi ponúka EPM7064STC100-7 výnimočnú flexibilitu pre integráciu do rôznych návrhov obvodov.Podpora úrovní logiky 3,3 V aj 5 V umožňuje plynulú kompatibilitu s rôznymi systémovými napätiami, čím sa eliminuje potreba ďalších radičov na úrovni napätia.Táto adaptabilita je vhodná pre aplikácie v prostrediach zmiešaného napätia, čím sa zabezpečuje širokú uplatniteľnosť vo vložených systémoch, priemyselných kontrolách a komunikačných sieťach.

• Programovateľnosť v systéme (ISP): Jednou z výhod EPM7064STC100-7 je jeho 5,0 V programovateľnosť systému (ISP), ktorá je uľahčená prostredníctvom IEEE STD.1149.1 rozhranie JTAG.Táto funkcia umožňuje preprogramovať a modifikovať logické funkcie bez toho, aby ste sa odhodili alebo fyzicky odstránili zariadenie, zjednodušenie údržby, ladenia a iteratívneho vývoja.Schopnosť ISP znižuje prestoje a zvyšuje flexibilitu aktualizácií firmvéru, vďaka čomu je neoceniteľná pre dynamické a rekonfigurovateľné digitálne návrhy.

EPM7064STC100-7 CAD modely

Symbol EPM7064stc100-7

EPM7064stc100-7 stopa

EPM7064STC100-7 3D model

Bloková schéma EPM7064STC100-7

Ten Bloková schéma EPM7064STC100-7 ukazuje, ako sú logické prvky čipu pripojené a kontrolované.Má štyri bloky logických polí (laboratóriá), označené A, B, C a D, z ktorých každý obsahuje 16 makrocellov.Tieto makrocelly vykonávajú logické funkcie a spájajú sa prostredníctvom programovateľného prepojenia (PIA), ktoré umožňuje flexibilné smerovanie signálov.Každé laboratórium je prepojené s I/O riadiacim blokom, pričom sa spracúva až 16 vstupných/výstupných kolíkov na laboratórium.Diagram tiež zobrazuje globálne riadiace signály (GCLK1, GCLK2, OE1 a GCLRN), ktoré pomáhajú spravovať funkcie prekladania a resetovania pre čip.Niektoré logické brány tieto signály spracúvajú skôr, ako dosiahnu rôzne časti systému.Návrh EPM7064STC100-7 umožňuje jeho používanie v rôznych programovateľných logických aplikáciách, ako sú štátne stroje, dekódovanie adries a ďalšie digitálne obvody na mieru.Jeho flexibilné prepojenia zabezpečujú efektívny prietok signálu a spoľahlivú prevádzku.

Špecifikácie EPM7064STC100-7

|

Typ |

Parameter |

|

Výrobca |

Alterna/Intel |

|

Séria |

Max® 7000s |

|

Balenie |

Podnos |

|

Stav |

Zastaraný |

|

Programovateľný typ |

V systéme programovateľné |

|

Čas oneskorenia TPD (1) max |

7,5 ns |

|

Dodávka napätia - vnútorná |

4,75 V ~ 5,25V |

|

Počet logických prvkov/blokov |

4 |

|

Počet makrocellov |

64 |

|

Počet brán |

1250 |

|

Počet I/O |

68 |

|

Prevádzková teplota |

0 ° C ~ 70 ° C (TA) |

|

Montáž |

Povrchová montáž |

|

Balenie |

100-tqfp |

|

Balík dodávateľských zariadení |

100-TQFP (14x14) |

|

Základné číslo produktu |

EPM7064 |

EPM7064STC100-7 Sekvencia programovania v systéme (ISP)

EPM7064STC100-7, časť rodiny CPLD MAX 7000S, sleduje šesťstupňovú sekvenciu programovania v systéme (ISP), aby sa zabezpečila správna konfigurácia.Tento proces vám umožňuje programovať zariadenie bez toho, aby ste ho odstránili z dosky obvodu.Proces ISP zahŕňa pokyny, adresy, adresy a údaje prostredníctvom kolíka TDI (Test Data in) a pri získavaní odpovedí prostredníctvom kolíka TDO (Test Data Out).

Prvá fáza, Zadajte ISP, zaisťuje, že I/O PINS hladko prechádzajú z užívateľského režimu do režimu ISP a vyžaduje približne 1 ms.Nasleduje Skontrolovať ID, kde je kremíkové ID zariadenia načítané, aby sa potvrdil správny cieľ.Ďalej Vymazať Posuny štádia v pokynoch vymaže a aplikuje 100ms erase impulz, čím vyčistí všetky existujúce údaje v bunkách EEPROM.Ten Program Nasleduje fáza, kde sa adresy a údaje postupne presúvajú do zariadenia a použijú programovacie impulzy na konfiguráciu buniek EEPROM.Každá adresa musí byť naprogramovaná individuálne, vďaka čomu je tento krok časovo náročný v závislosti od počtu buniek EEPROM v zariadení.

Po dokončení programovania, Preveriť Fáza zaisťuje, že údaje boli správne uložené.Tu sa na bunky EEPROM používajú čítané impulzy a získané údaje sa porovnávajú s očakávanými hodnotami.Ak sa nájdu nezrovnalosti, môže byť potrebné preprogramovanie.Nakoniec Výstup ISP Fáza zaisťuje, že I/O PINS prechádzajú späť do užívateľského režimu, čo si vyžaduje ďalšie 1 ms.Celkový čas programovania alebo overovania je ovplyvnený dvoma hlavnými faktormi: čas impulzu, ktorý sa vyžaduje na vymazanie, programovanie a čítanie EEPROM, a čas presunu, ktorý závisí od frekvencie TCK (testovacie hodiny) a počtu cyklov potrebných na prenos pokynov, adries a údajov.Pretože rôzne zariadenia spôsobené ISP majú rôzny počet buniek EEPROM, celkové pevné aj variabilné časy sú pre každé zariadenie jedinečné.Celkový čas ISP sa môže vypočítať ako funkcia frekvencie TCK, počtu cieľových zariadení a architektúry EEPROM.

Aplikácie EPM7064STC100-7

Zabudované systémy

EPM7064STC100-7 sa široko používa v aplikáciách vložených systémov, kde slúži ako flexibilné programovateľné logické riešenie na riadenie rôznych periférnych zariadení, spracovateľských signálov a implementáciu vlastných protokolov.Jeho schopnosť prepojiť sa s mikrokontrolérmi a senzormi umožňuje optimalizovať výkon systému pri zachovaní kompaktnej stopy.Vďaka svojej vysokorýchlostnej prevádzke a nízkej spotrebe energie je vynikajúcou voľbou pre zabudované aplikácie, ktoré si vyžadujú spoľahlivosť a efektívnosť.

Spracovanie digitálneho signálu (DSP)

Pri spracovaní digitálneho signálu hrá EPM7064STC100-7 úlohu pri implementácii filtrov, modulácie signálu a rôznych matematických funkcií.Vďaka rýchlemu prepínajúcemu rýchlostiam a nízkym oneskorením šírenia je vhodný na manipuláciu s vysokofrekvenčnými úlohami spracovania údajov, čím sa zabezpečí minimálna latencia pri konverzii a manipulácii signálu.Bežne sa používa pri spracovaní zvuku, telekomunikáciám a radarovým systémom.

Dátová komunikácia

EPM7064STC100-7 sa vo veľkej miere používa v sieťových a dátových komunikačných systémoch kvôli svojej schopnosti zvládnuť logické operácie, ako je smerovanie údajov, vyrovnávanie a korekcia chýb.Jeho programovateľné vstupno -výstupné schopnosti umožňujú prispôsobiť sa rôznym komunikačným protokolom, čo z neho robí cennú súčasť v prepínačoch Ethernet, smerovačoch a telekomunikačnej infraštruktúre.Jeho podpora pre programovateľnosť v systéme (ISP) tiež umožňuje aktualizácie v teréne a zlepšuje prispôsobivosť v dynamických sieťových prostrediach.

Priemyselná automatizácia

Priemyselné aplikácie si vyžadujú vysokú spoľahlivosť, trvanlivosť a nízku spotrebu energie, vďaka čomu je EPM7064STC100-7 preferovanou voľbou pre programovateľné logické ovládače (PLC), systémy riadenia motora a automatizované testovacie zariadenia.Vďaka svojej programovateľnosti v systéme založených na JTAG poskytuje schopnosť vylepšiť procesy automatizácie bez toho, aby si vyžadovalo fyzické odstránenie alebo redizajn.Jeho univerzálnosť v kompatibilite napätia je tiež vhodná na prepojenie so širokou škálou senzorov a ovládačov používaných v priemyselnom prostredí.

EPM7064STC100-7 Podobné časti

EPM7064STC100-7 Výhody

Programovateľnosť v systéme (ISP)

Jednou z najväčších výhod EPM7064STC100-7 je jej schopnosť preprogramovať sa, zatiaľ čo je stále namontovaná v systéme.Tým sa eliminuje potreba odstránenia čipu pre aktualizácie, skrátenie času údržby a zlepšenie účinnosti.Môžete implementovať úpravy dizajnu bez prerušenia výroby, čím sa z neho stane nákladovo efektívne riešenie pre dlhodobé projekty.

Vysokorýchlostný výkon

Zariadenie podporuje vysokú internú prevádzkovú frekvenciu až do 166,7 MHz, čo umožňuje rýchle spracovanie údajov a časy odozvy.Vďaka tomu je ideálne pre aplikácie vyžadujúce spracovanie signálu, riadenie logiky a vysokorýchlostné rozhranie, zabezpečujúc plynulejšiu a spoľahlivejšiu prevádzku systému.

Všestranná podpora I/O

S až 68 konfigurovateľnými I/O PIN a kompatibilita s viacerými úrovňami napätia (3,3 V, 5V a tolerantné možnosti pre 2,5 V, 3,3 V a 5V) ponúka EPM7064STC100-7 flexibilitu v návrhu systému.Umožňuje plynulú integráciu do rôznych obvodov a podporuje prostredia zmiešaného napätia, čím sa znižuje problémy s kompatibilitou s inými komponentmi.

Spoľahlivá prevádzka v prostrediach

EPM7064STC100-7, navrhnutá tak, aby fungovala v teplotnom rozsahu od 0 ° C až 70 ° C, zaisťuje konzistentnú a stabilnú prevádzku v rôznych podmienkach.Táto spoľahlivosť z nej robí preferovanú voľbu pre aplikácie, v ktorých je potrebná environmentálna stabilita, ako napríklad priemyselná automatizácia, telekomunikácie a zabudované riadiace systémy.

EPM7064STC100-7 Schéma obalu

EPM7064STC100-7 je CPLD (komplexné programovateľné logické zariadenie) zo série Max 7000S Altera, umiestneného v 100-kolíkovom tenkom štvorkolskom plochom štvorkolke (TQFP-100).Tento typ balíka je navrhnutý pre aplikácie na povrchové namáhanie a ponúka rovnováhu s vysokou hustotou kolíkov a kompaktnej veľkosti.Ten schéma Nasleduje schéma číslovania proti smeru hodinových ručičiek, pričom kolík 1 sa nachádza v ľavom hornom rohu balenia.Pohybujúc sa proti smeru hodinových ručičiek, prvých 25 kolíkov zaberá ľavú stranu, kolíky 26 až 50 sú umiestnené pozdĺž spodného okraja, kolíky 51 až 75 pokračujú pozdĺž pravej strany a kolíky 76 až 100 sú rozložené pozdĺž horného okraja.Ten Balík TQFP-100 Vlastnosti tenkých vodičov siahajúcich smerom von od všetkých štyroch strán plochého štvorcového tela.Táto konštrukcia zvyšuje kompatibilitu s povrchom a pri zachovaní dostatočného rozstupu PIN pre ľahkú spájkovanie a montáž.Pitch olovu (vzdialenosť medzi susednými kolíkmi) je zvyčajne 0,5 mm, pričom optimalizuje integritu signálu a zároveň minimalizuje celkovú stopu.

EPM7064STC100-7 Výrobca

EPM7064STC100-7 je CPLD (komplexné programovateľné logické zariadenie) pôvodne vyvinuté spoločnosťou Altera, polovodičovou spoločnosťou, ktorá je známa svojimi programovateľnými logickými riešeniami.V roku 2015, Zamerať Získaná spoločnosť Altera, integráciu svojich produktových radov FPGA a CPLD do Group Group Solutions spoločnosti Intel (PSG).Odvtedy je EPM7064STC100-7 označený ako Intel, hoci bol označený ako zastaraný.Spoločnosť Intel ako výrobca udržiavala starú podporu pre CPLD Series MAX® 7000S vrátane tohto modelu, pričom sa postupne presúvalo na moderné FPGA a programovateľné logické technológie.

Záver

EPM7064STC100-7 spája zložité funkcie, rýchly výkon a ľahké aktualizácie v jednom čipe, čo dokazuje jeho hodnotu v náročných digitálnych nastaveniach.Táto príručka ukázala, ako to funguje, na čo sa používa a ako zapadá do rôznych elektronických systémov.Pomáha, aby zariadenia fungovali hladko a efektívne, čo dokazuje, že pre mnohé aplikácie je stále veľmi užitočné.Táto príručka poskytuje jasný pohľad na to, ako môže EPM7064STC100-7 pomôcť efektívne zlepšiť elektronické návrhy a operácie systému.

Datasheet pdf

EPM7064STC100-7 DataShety:

O nás

ALLELCO LIMITED

Čítaj viac

Rýchly dopyt

Zašlite prosím dotaz, okamžite odpovieme.

často kladené otázky [FAQ]

1. Ako je výkonnosť šírenia 7,5 NS vo výkone nárazového obvodu EPM7064STC100-7?

Oneskorenie šírenia 7,5ns zaisťuje spracovanie signálu s nízkou latenciou, vďaka čomu je tento CPLD vhodný pre vysokorýchlostné aplikácie, ako je spracovanie digitálneho signálu (DSP), komunikačné systémy a priemyselná automatizácia, ktoré si vyžadujú presné riadenie načasovania.

2. Dá sa EPM7064STC100-7 naprogramovať pomocou moderných vývojových nástrojov?

Áno, dá sa naprogramovať pomocou softvéru Intel Quartus II (predtým Altera Quartus) spolu s príslušným programátorom JTAG.Podpora pre staršie CPLD, ako je EPM7064STC100-7, však môže byť obmedzená v novších verziách Quartus, takže možno budete musieť použiť staršie verzie, ako je Quartus II 13.0 SP1, ktoré stále podporujú zariadenia série MAX® 7000S.

3. Podporuje EPM7064STC100-7 prostredia zmiešaného napätia?

Áno, podporuje úroveň logiky 3,3 V aj 5 V, vďaka čomu je kompatibilná so širokou škálou digitálnych obvodov.Táto flexibilita je užitočná pri prepojení starších 5V komponentov s modernými systémami 3,3 V bez ďalších obvodov posunu na úrovni.

4. Aká je najlepšia metóda na riešenie problémov s dizajnom založeným na EPM7064STC100-7?

Na riešenie problémov môžete na monitorovanie signálov použiť logický analyzátor Quartus SignalTap II alebo externé osciloskopy a logické analyzátory.Ak ladenie problémov s programovaním JTAG, uistite sa, že pripojenia TDI, TDO, TCK a TMS sú správne a že používate kompatibilný programátor USB Blaster alebo BYTEBLOSTERMV.

5. Môžem naprogramovať EPM7064STC100-7 bez toho, aby som ho odstránil z mojej dosky s obvodom?

Áno.5.0V Programovateľnosť v systéme (ISP) prostredníctvom JTAG (IEEE 1149.1) vám umožňuje preprogramovať zariadenie, kým zostáva v systéme.Vďaka tomu je aktualizácie firmvéru, ladenie a testovanie oveľa efektívnejšie v porovnaní s tradičnými CPLDS.

Kompletný sprievodca k odporu 10K: farebný kód, aplikácie a používanie obvodov

na 2025/03/10

Kondenzátory verzus batérie: Čo je najlepšie pre vaše energetické potreby?

na 2025/03/7

Populárne príspevky

-

Komplexné súpravy inštrukcií: Ako zmenili výpočty?

na 8000/04/19 147781

-

USB-C Pinout a funkcie

na 2000/04/19 112052

-

Pomocou Xilinx Unified Simulation Primitive: Komplexný sprievodca dizajnom a simuláciou FPGA

na 1600/04/19 111352

-

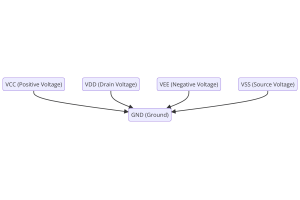

Napájacie napätia v elektronike: Význam VCC, VDD, VEE, VSS a GND

na 0400/04/19 83807

-

Sprievodca konektorom RJ45: Pinout, kábly, typy káblov a použitia

na 1970/01/1 79613

-

Konečný sprievodca k farebným kódom drôtu v moderných elektrických systémoch

Spôsob, akým naše elektrické systémy používajú farby, nie je len pre vzhľad.Každá farba drôtu teraz označuje špecifickú funkciu, čo uľahčuje správne identifikáciu a spracovanie elektrických kompone...na 1970/01/1 66992

-

Sprievodca čistením ventilu: funkcia, príznaky, testovanie a výmena za optimálny výkon motora

Čistý ventil je kľúčovou súčasťou systému automobilu, ktorý pomáha udržiavať vzduch čistý riadením výparov paliva skôr, ako môžu uniknúť do atmosféry.To nielen pomáha životnému prostrediu znížením ...na 1970/01/1 63117

-

Kvalita (Q) Faktor: Rovnice a aplikácie

Faktor kvality alebo „Q“ je dôležitý pri kontrole, ako dobre induktory a rezonátory pracujú v elektronických systémoch, ktoré používajú rádiové frekvencie (RF).'Q' meria, ako dobre obvod minimalizu...na 1970/01/1 63051

-

Dosiahnutie maximálneho výkonu s maximálnou vetou prenosu energie

Maximálna veta prenosu energie vysvetľuje, ako energia zo zdroja, napríklad batéria alebo generátor, tečie na pripojené zaťaženie.Zobrazuje presnú podmienku, keď zaťaženie prijíma najviac energie.T...na 1970/01/1 54097

-

Špecifikácie batérie A23 a kompatibilita

Batéria A23 je malá batéria v tvare valca s vysokým napätím.Nazýva sa tiež 23A, 23ae alebo MN21, beží na 12 voltoch a oveľa vyšších ako batérie AA alebo AAA.Vďaka jeho špeciálnemu dizajnu ...na 1970/01/1 52202