EP1C4F400C8 FPGA: Funkcie, špecifikácie, programovanie a alternatívy

Ak pracujete s programovateľnou logikou, EP1C4F400C8 vám poskytne praktickú rovnováhu výkonnosti a nákladov.V tomto článku sa dozviete, čo je tento FPGA, jej kľúčové funkcie, ako je logická kapacita, pamäť a I/O možnosti a ako jej štruktúra podporuje spoľahlivý dizajn.Uvidíte tiež jeho špecifikácie, aplikácie v systémoch, proces programovania a ako sa porovnáva s podobnými časťami.Katalóg

Čo je EP1C4F400C8?

Ten EP1C4F400C8 je členom spoločnosti Intel (predtým Altera's) Cyclone FPGA Family, navrhnutá ako nákladovo efektívne a spoľahlivé programovateľné logické riešenie.Toto zariadenie postavené na procese 0,13 µm SRAM, ponúka miernu logickú hustotu a flexibilné možnosti I/O v rámci kompaktného balíka FBGA-400.Rodina cyklónov, ktorá zahŕňa zariadenia ako EP1C3, EP1C6, EP1C12 a EP1C20, bola vytvorená na vyváženie výkonu a cenovej dostupnosti pre škálovateľné návrhy, čo umožňuje ľahkú migráciu medzi úrovňami hustoty a balíčkami.Známy pre stabilitu a široké prijatie, zostáva dôveryhodnou voľbou v starších dizajnoch.

Hľadáte EP1C4F400C8?Kontaktujte nás a skontrolujte aktuálne zásoby, dodací čas a ceny.

EP1C4F400C8 CAD modely

Symbol EP1C4F400C8

EP1C4F400C8 stopa

EP1C4F400C8 3D model

Funkcie EP1C4F400C8

• Logická kapacita

EP1C4F400C8 ponúka približne 4 000 logických prvkov usporiadaných do 400 logických blokov (LABS).Vďaka tomu je vhodné pre návrhy stredného rozsahu, ktoré si pri zachovaní nákladovej efektívnosti vyžadujú miernu hustotu logiky.

• Vložená pamäť

Integruje približne 76,5 kbits vloženej pamäte.Tento interný RAM podporuje vyrovnávanie údajov, úložisko a malé pamäťové funkcie, čím znižuje potrebu komponentov externej pamäte v mnohých dizajnoch.

• Vysoký počet I/O

Zariadenie poskytuje 301 užívateľsky konfigurovateľné vstupno-výstupné kolíky vo svojom balíku FBGA s 400 loptičkami.Tento vysoký počet kolíkov umožňuje bohaté pripojenie pre komplexné systémy vyžadujúce viac periférnych rozhraní.

• Široká podporná I/O Normy

Podporuje viac I/O štandardov vrátane LVTTL, LVCMOS, SSTL-2, SSTL-3 a diferenciálnych LVD.Táto flexibilita umožňuje FPGA prepojiť priamo s rôznymi modernými logickými rodinami a pamäťovými zariadeniami.

• Vysokorýchlostná diferenciálna signalizácia

S podporou LVD až 640 Mbps, FPGA spracováva rýchle požiadavky na prenos údajov.Vďaka tomu je praktické pre aplikácie, ako sú vysokorýchlostné komunikačné spojenia a rýchle digitálne rozhrania.

• Správa hodín s PLLS

Čip integruje dve fázové slučky (PLLS) a osem globálnych hodinových sietí.Tieto funkcie umožňujú presné generovanie hodín, násobenie a reguláciu jitter pre aplikácie na časovanie.

• Operácia jadra s nízkym napätím

Pracuje pri nominálnom 1,5 V jadrovom napätí, zariadenie vyvažuje výkon s nižšou spotrebou energie.Táto hladina napätia bola optimalizovaná pre technológiu CMOS 0,13 um použitú pri jej výrobe.

• Flexibilné I/O napätie

FPGA podporuje napätie I/O 1,5 V, 1,8 V, 2,5 V a 3,3 V v rôznych bankách.Táto univerzálnosť jej umožňuje prepojiť sa s starými a modernými komponentmi systému.

• Konfigurácia založená na SRAM

Rovnako ako iné cyklóny FPGA, je založený na SRAM a vyžaduje rekonfiguráciu pri každom zapnutí.Toto poskytuje flexibilitu pre aktualizácie, ale tiež si vyžaduje externé konfiguračné zariadenie alebo ovládač.

• Podpora kompresie bitov

EP1C4F400C8 podporuje zaťaženie komprimovaného bitov počas konfigurácie.To znižuje požiadavky na externú pamäť a urýchľuje časy konfigurácie.

• Súlad PCI

Zahŕňa zabudovanú podporu pre štandardy PCI (33/66 MHz, 32/64-bit).Táto funkcia umožňuje, aby bolo zariadenie priamo integrované do systémov vyžadujúcich prepojenie PCI bez ďalšej preklenutej logiky.

Štruktúra cyklónu

Schéma zobrazuje štruktúru logického poľa bloku (LAB) použitá v cyklónových FPGA, ako je EP1C4F400C8.Každé laboratórium sa pripája k sieti vzájomných prepojení: prepojenia riadkov, prepojenia stĺpcov a lokálnych prepojení, ktoré smerujú signál medzi logickými prvkami a inými blokmi.Prepojenia priameho spojenia poskytujú rýchle a nízko-latenčné cesty k susedným laboratóriám, čím sa zlepšuje výkon načasovania v dráhach signálu.Táto architektúra je dôležitá, pretože vyvažuje flexibilitu smerovania s účinnosťou, čo umožňuje FPGA zvládnuť zložité vzory a zároveň udržiavať optimalizovanú rýchlosť a oblasť.

Cyklón I/O Banks Diagram

Schéma ilustruje I/O Bank štruktúru cyklónových FPGA, ako je napríklad EP1C4F400C8.Zariadenie je rozdelené do štyroch vstupno -výstupných bánk, z ktorých každá je poháňaná vlastnou zásobovacou zbernicou, čo umožňuje miešanie rôznych štandardov napätia v rámci jedného FPGA.Všetky banky podporujú širokú škálu I/O štandardov vrátane LVTTL, LVCMOS, LVDS, RSD a SSTL, zatiaľ čo banky 1 a 3 podporujú tiež 3,3-V PCI pre kompatibilitu so starými systémami.Táto flexibilná architektúra I/O je dôležitá, pretože umožňuje bezproblémovú integráciu s rôznymi externými zariadeniami a rozhraniami, vďaka čomu je FPGA prispôsobiteľná rôznym aplikáciám.

Špecifikácie EP1C4F400C8

|

Typ |

Parameter |

|

Výrobca |

Alterna/Intel |

|

Séria |

Cyklón® |

|

Balenie |

Podnos |

|

Stav |

Zastaraný |

|

Počet laboratórií/CLB |

400 |

|

Počet logických prvkov/buniek |

4000 |

|

Celkový baranový kúsok |

78 336 |

|

Počet I/O |

301 |

|

Napätie - napájanie |

1,425V ~ 1,575V |

|

Montáž |

Povrchová montáž |

|

Prevádzková teplota |

0 ° C ~ 85 ° C (TJ) |

|

Balenie |

400-bGA |

|

Balík dodávateľských zariadení |

400-FBGA (21 × 21) |

|

Základné číslo produktu |

EP1C4 |

Aplikácie EP1C4F400C8

1. Spracovanie digitálneho signálu (DSP)

EP1C4F400C8 môže byť naprogramovaný tak, aby vykonával úlohy, ako je filtrovanie, FFT a modulácia signálu.Vďaka kombinácii logických prvkov a zabudovanej pamäte je vhodná na vysokorýchlostné spracovanie.To mu umožňuje nahradiť tradičné čipy DSP flexibilným riešením FPGA, ktoré je možné preprogramovať pre rôzne algoritmy.

2. Vstavané a riadiace systémy

V priemyselných a zabudovaných systémoch sa tento FPGA často používa na implementáciu vlastných radičov, sekvencerov a štátnych strojov.Jeho rekonfigurovateľná logika umožňuje prispôsobiť správanie hardvéru presne podľa potreby systému.Integráciou logiky riadenia do FPGA sa zníži počet externých komponentov, čím sa zvyšuje spoľahlivosť a zníženie nákladov.

3. Komunikácia a premostenie rozhrania

Zariadenie podporuje viac vstupno -výstupných štandardov a môže pôsobiť ako most medzi rôznymi komunikačnými protokolmi.Často sa používa na prepojenie PCI, LVD, SDRAM a ďalších rozhraní v systéme.Vďaka tomu je veľmi užitočné pri sieťových zariadeniach, vložených ovládačoch a konverziách odkazu na moderné rozhranie.

4. Získavanie a spracovanie údajov

S vysokou dostupnosťou I/O a flexibilnej pamäte je EP1C4F400C8 vhodný pre systémy zberu údajov.Môže priamo prepojiť s ADC a senzormi, spracovať údaje v čase a pripraviť ich na ukladanie alebo prenos.Takéto aplikácie sú bežné v lekárskych nástrojoch, testovacích zariadeniach a vedeckých meracích zariadeniach.

EP1C4F400C8 Podobné časti

|

Špecifikácia |

EP1C4F400C8 |

EP1C4F400C8N |

EP1C4F400C8NAA |

EP1C4F400C6N |

EP1C4F324C8N |

EP1C4T144C8N |

|

Výrobca |

Altera (Intel) |

Altera (Intel) |

Altera (Intel) |

Altera (Intel) |

Altera (Intel) |

Altera (Intel) |

|

Rodina FPGA |

Cyklón (EP1C4) |

Cyklón (EP1C4) |

Cyklón (EP1C4) |

Cyklón (EP1C4) |

Cyklón (EP1C4) |

Cyklón (EP1C4) |

|

Logické prvky (LES) |

4 000 |

4 000 |

4 000 |

4 000 |

4 000 |

4 000 |

|

Vstavaná pamäť (bity) |

~ 76,5 kbits |

~ 76,5 kbits |

~ 76,5 kbits |

~ 76,5 kbits |

~ 76,5 kbits |

~ 76,5 kbits |

|

PIN/O |

301 |

301 |

301 |

301 |

249 |

97 |

|

Balenie |

400-FBGA |

400-FBGA |

400-FBGA |

400-FBGA |

324-FBGA |

144-tqfp |

|

Rýchlosť |

C8 |

C8 |

C8 |

C6 (rýchlejšie) |

C8 |

C8 |

|

Napätie jadra |

1,5 V |

1,5 V |

1,5 V |

1,5 V |

1,5 V |

1,5 V |

|

Prevádzková teplota.Rozsah |

0 ° C ~ 85 ° C |

0 ° C ~ 85 ° C |

0 ° C ~ 85 ° C |

0 ° C ~ 85 ° C |

0 ° C ~ 85 ° C |

0 ° C ~ 85 ° C

|

EP1C4F400C8 Programovacie kroky

Predtým, ako budete môcť použiť FPGA EP1C4F400C8, musíte svoj návrh načítať do zariadenia.Programovanie zahŕňa konfiguráciu FPGA pomocou súboru Bitstream, takže vie, ako sa správať ako zamýšľaný obvod.

1. Vyberte konfiguračnú schému a nastaviť kolíky MSEL

Začnete výberom konfiguračnej schémy, ktorá najlepšie vyhovuje vášmu nastaveniu, napríklad aktívny sériový, pasívny seriál alebo JTAG.To sa deje nastavením kolíkov MSEL na konkrétne úrovne logiky pred zapnutím.Každý režim používa rôzne kolíky a protokoly, takže musíte potvrdiť kompatibilitu s nástrojmi navrhovania a konfiguračnou pamäťou.Správny výber tu zaisťuje hladký proces konfigurácie.

2. Použite napájanie a inicializujte zariadenie

Ďalej zapnite jadro FPGA a I/O Rails v rámci určených rozsahov napätia.Počas spustenia udržiavajte špendlík NCONFIG na nízkej úrovni, aby ste zariadenie držali v resetovaní, až kým napájacie napätie nebude stabilné.Akonáhle je stabilný, uvoľníte reset a zariadenie signalizuje pripravenosť riadením špendlíka Nstatus.To zaručuje, že FPGA je správne inicializovaná pred začiatkom konfigurácie.

3. Prejdite konfiguračný bitstream

V tejto fáze pošlete súbor konfiguračného dátového súboru (BitStream) do FPGA pomocou vybranej schémy.V aktívnom sériovom alebo pasívnom sériovom režime pochádza Bitstream z externého pamäťového zariadenia, zatiaľ čo JTAG umožňuje priame programovanie prostredníctvom kábla.Zariadenie nepretržite číta v konfiguračných údajoch, kým nebude dokončené.Váš dizajnový softvér generuje tento BitStream tak, aby zodpovedal vašim logickým požiadavkám.

4. Potvrďte úspešnú konfiguráciu (Conf_done)

Keď FPGA dokončí načítanie, uplatňuje kolík Conf_Done, aby ukázal, že konfiguračné údaje boli úspešne prijaté.Súčasne zariadenie vykonáva internú inicializáciu, ako sú zúčtovacie registre a aktivácia I/O.Ak Conf_Done nedokáže ísť vysoko, zvyčajne to znamená, že konfiguračné údaje alebo nastavenie majú chybu.Sledovanie tohto PIN je najjednoduchším spôsobom, ako overiť, či je proces dokončený.

5. Vykonajte voliteľnú rekonfiguráciu systému v systéme

Nakoniec máte možnosť aktualizovať alebo preprogramovať FPGA bez toho, aby ste ju odstránili z dosky.Pomocou JTAG alebo zabudovaného ovládača môžete priamo načítať nový BitStream, ktorý je užitočný pre aktualizácie firmvéru.Táto flexibilita vám umožňuje upravovať, ladiť alebo aktualizovať systém aj po nasadení.Zaisťuje, že váš dizajn založený na FPGA sa môže časom prispôsobiť meniacim sa požiadavkám.

EP1C4F400C8 Výhody a nevýhody

Výhody

• nákladovo efektívna voľba pre návrhy stredného rozsahu

• Vysoký počet I/O v porovnaní s podobnými zariadeniami hustoty

• Flexibilné napätie a štandardná podpora I/O

• Podporované zrelými nástrojmi a dokumentáciou

• Použitie nižšej energie ako staršie generácie FPGA

Nevýhody

• Zastarané s obmedzenou dlhodobou dostupnosťou

• Nižšia logika a kapacita pamäte vs. moderné FPGA

• Pomalšia prevádzková rýchlosť a výkon I/O

• Vyžaduje externú pamäť na konfiguráciu pri zapnutí

• Chýbajú pokročilé funkcie, ako sú bloky DSP a vysokorýchlostné transceivery

EP1C4F400C8 rozmery obalu

|

Typ |

Parameter |

|

Typ balíka |

FBGA (pole Fine-Pitch Ball Grid Array) |

|

Počet loptičiek |

400 |

|

Pitch Lall (E) |

1,0 mm (typické pre cyklón EP1C4F400) |

|

Priemer lopty (B) |

0,45 mm (nominálne) |

|

Veľkosť obalu (D × E) |

21 mm × 21 mm |

|

Výška balíka (a) |

2,40 mm (max) |

|

Hrúbka substrátu (A2) |

~ 0,40 mm |

|

Hrúbka krytu plesne (A3) |

~ 1,90 mm |

|

Výška gule (A1) |

0,25 mm (nominálne) |

|

Roh pin A1 |

Označené na orientáciu |

|

Usporiadanie poľa |

Mriežka 20 × 20 (s rohovými loptičkami) |

|

Montáž |

Povrchová držiak (SMD) |

Výrobca EP1C4F400C8

EP1C4F400C8 bol pôvodne vyrobený Spoločnosť Altera Corporation, priekopníkom v programovateľných logických zariadeniach a technológii FPGA.V roku 2015 získala Altera Spoločnosť Intel Corporationa produktová rada sa stala súčasťou skupiny Intel Programmable Solutions Group (PSG).Spoločnosť Intel dnes podporuje tieto staré zariadenia Alterra a zároveň sa zameriava na vývoj na novšie rodiny FPGA, zabezpečuje kontinuitu existujúcich používateľov a rozvíjajú inovácie v programovateľnej logike.

Záver

EP1C4F400C8 vyniká ako nákladovo efektívny a všestranný FPGA, ktorý ponúka solídny výkon pre vzory stredného rozsahu.Vďaka svojim 4 000 logickým prvkom, vloženou pamäťou, rozsiahlou podporou I/O a kompatibilitou s viacerými štandardmi napätia a rozhrania poskytuje flexibilitu vo rôznych aplikáciách.Jeho architektúra, proces programovania a široká použiteľnosť v DSP, vložených systémoch a získavaní údajov z neho robia praktickú voľbu napriek svojmu staršiemu stavu.Aj keď chýbajú pokročilé funkcie, ktoré sa nachádzajú v novších zariadeniach a tváre obmedzenej dlhodobej dostupnosti, zostáva spoľahlivou možnosťou, ktorá hľadá osvedčené riešenia v škálovateľných dizajnoch FPGA.

Datasheet pdf

EP1C4F400C8 DataShety:

O nás

ALLELCO LIMITED

Čítaj viac

Rýchly dopyt

Zašlite prosím dotaz, okamžite odpovieme.

často kladené otázky [FAQ]

1. Aké nástroje sú potrebné na programovanie EP1C4F400C8?

Potrebujete softvér spoločnosti Intel Quartus (predtým Altera Quartus II) spolu s podporovaným programovacím káblom, ako je USB-Blaster.Tieto nástroje vám umožňujú vytvoriť BitStream a načítať ho do FPGA.

2. Môže EP1C4F400C8 zvládnuť aplikácie PCI priamo?

Áno, má vstavaný súlad s štandardmi PCI (33/66 MHz, 32/64-bitové), vďaka čomu je vhodný pre integráciu systému založenú na PCI bez toho, aby vyžadoval ďalšiu premostenú logiku.

3. Čo sa stane, ak EP1C4F400C8 zlyhá počas konfigurácie?

Ak konfigurácia zlyhá, kolík Conf_Done nebude presadiť vysoko.Zvyčajne to poukazuje na chybu v súbore Bitstream, sekvenovanie napätia alebo nastavenie PIN a malo by sa skontrolovať vo vašom konštrukčnom toku.

4. Môže rozhranie EP1C4F400C8 priamo s pamäťou DDR?

Podporuje niekoľko I/O štandardov, ale nemá natívne rozhrania DDR, ako je moderné FPGA.Môžu byť potrebné ďalšie úvahy o návrhu alebo premostené komponenty.

5. Ako porovnáva EP1C4F400C8 s novšími FPGA?

V porovnaní s modernými zariadeniami má EP1C4F400C8 nižšiu rýchlosť, menšiu hustotu logiky a menej pokročilých funkcií.Zostáva však nákladovo efektívnou voľbou pre stabilné dizajny stredného rozsahu, v ktorých sa nevyžaduje špičkový výkon.

EPM3256AFC256-7 Prehľad CPLD: Funkcie, pinout, programovanie a aplikácie

na 2025/10/3

ADG432BR Analógový prepínač IC: Špecifikácie, pinout, alternatívy a datashet

na 2025/10/2

Populárne príspevky

-

Komplexné súpravy inštrukcií: Ako zmenili výpočty?

na 8000/04/18 147772

-

USB-C Pinout a funkcie

na 2000/04/18 112009

-

Pomocou Xilinx Unified Simulation Primitive: Komplexný sprievodca dizajnom a simuláciou FPGA

na 1600/04/18 111351

-

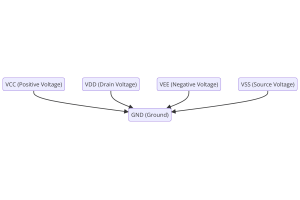

Napájacie napätia v elektronike: Význam VCC, VDD, VEE, VSS a GND

na 0400/04/18 83768

-

Sprievodca konektorom RJ45: Pinout, kábly, typy káblov a použitia

na 1970/01/1 79565

-

Konečný sprievodca k farebným kódom drôtu v moderných elektrických systémoch

Spôsob, akým naše elektrické systémy používajú farby, nie je len pre vzhľad.Každá farba drôtu teraz označuje špecifickú funkciu, čo uľahčuje správne identifikáciu a spracovanie elektrických kompone...na 1970/01/1 66960

-

Sprievodca čistením ventilu: funkcia, príznaky, testovanie a výmena za optimálny výkon motora

Čistý ventil je kľúčovou súčasťou systému automobilu, ktorý pomáha udržiavať vzduch čistý riadením výparov paliva skôr, ako môžu uniknúť do atmosféry.To nielen pomáha životnému prostrediu znížením ...na 1970/01/1 63100

-

Kvalita (Q) Faktor: Rovnice a aplikácie

Faktor kvality alebo „Q“ je dôležitý pri kontrole, ako dobre induktory a rezonátory pracujú v elektronických systémoch, ktoré používajú rádiové frekvencie (RF).'Q' meria, ako dobre obvod minimalizu...na 1970/01/1 63040

-

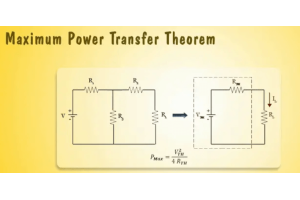

Dosiahnutie maximálneho výkonu s maximálnou vetou prenosu energie

Maximálna veta prenosu energie vysvetľuje, ako energia zo zdroja, napríklad batéria alebo generátor, tečie na pripojené zaťaženie.Zobrazuje presnú podmienku, keď zaťaženie prijíma najviac energie.T...na 1970/01/1 54097

-

Špecifikácie batérie A23 a kompatibilita

Batéria A23 je malá batéria v tvare valca s vysokým napätím.Nazýva sa tiež 23A, 23ae alebo MN21, beží na 12 voltoch a oveľa vyšších ako batérie AA alebo AAA.Vďaka jeho špeciálnemu dizajnu ...na 1970/01/1 52184