Komplexný sprievodca Testbenches: Nástroje a techniky overovania digitálneho systému

Táto príručka skúma testybenches, kľúčový nástroj na overenie softvéru, ktorý simuluje podmienky na testovanie vstupov a overovanie výstupov.Testbenches zohrávajú úlohu pri identifikácii chýb na začiatku vývoja, čím sa zlepšuje spoľahlivosť softvéru.Vďaka praktickým príkladom a poznatkom tento článok zdôrazňuje ich použitie, techniky a význam pri budovaní silných a efektívnych digitálnych systémov.Katalóg

Úloha testovacích zariadení pri validácii digitálneho systému

Testbench je súčasťou procesu validácie digitálneho systému.Nie je to iba nástroj na generovanie vstupov a overovanie výstupov, slúži ako komplexný rámec, ktorý simuluje podmienky na vyhodnotenie spoľahlivosti, funkčnosti a správania digitálnych systémov pred ich nasadením v teréne.Vytvorením kontrolovaných prostredí pre systémy stresových testov so širokou škálou vstupných scenárov vám testybenches pomôže identifikovať potenciálne návrhy nedostatkov na začiatku životného cyklu vývoja, dlho predtým, ako sa systém uvedie do výroby.Toto včasné odhalenie chýb a zraniteľností je potrebné na zníženie nákladných chýb, zabezpečenie dodržiavania špecifikácií výkonnosti a zlepšenie celkovej spoľahlivosti systému.

Okrem overenia správnosti reakcií systému, testybenches zohrávajú úlohu pri hodnotení okrajových prípadov, problémov s načasovaním a mechanizmov spracovania chýb, čím sa zabezpečuje správne fungovanie systému aj za extrémnych alebo neočakávaných podmienok.Prostredníctvom automatizovaného testovania a simulácie prispievajú testovacie testy k vyššej kvalite softvéru, zlepšenému výkonu a kratším vývojovým cyklom tým, že umožňujú iteračné testovanie bez manuálneho zásahu.Slúžia ako ochrana proti zlyhaniam, ktoré by sa mohli vyskytnúť po nasadení, čím sa zabezpečuje robustnosť a spoľahlivosť digitálnych systémov.

Kľúčové komponenty testovania a ich funkcií

Aby ste lepšie pochopili, ako fungujú testy, je dôležité preskúmať komponenty, ktoré ich robia efektívnymi.Dobre vypracovaný testbench funguje riadením dvoch základných úloh: generovanie vstupov (stimuly) a overovaním výstupov.Podrobne preskúmajme každú komponent.

Generovanie stimulov

Generovanie stimulu zahŕňa vytvorenie súboru vstupných signálov, ktoré simulujú podmienky na testovanie správania digitálneho systému.Tieto vstupy musia byť presné aj realistické, aby sa zabezpečilo, že systém je podrobený rôznym scenárom, s ktorými by sa mohol v praxi stretnúť.Za príklad zvážte základný modul RAM.Testbench musí do modulu dodať konkrétne vstupy a sledovať jeho výstupy, aby sa zabezpečilo, že sa správa podľa očakávania.Kľúčové vstupy pre modul RAM zvyčajne zahŕňajú:

• CLK (hodiny): poháňa načasovanie systému.

• Addr (Address): Určuje, ktoré umiestnenie údajov má prístup.

• Wen (Enable Write): Ovláda, či sú údaje zapísané do pamäte.

• Dáta: Skutočné informácie, ktoré sú napísané do modulu.

Výstup, známy ako DataOut, predstavuje výsledok interných operácií modulu.Dôkladným skriptovaním, ako sa tieto vstupy dodávajú, a monitorovaním Dataout, môžete overiť, či systém funguje správne v rôznych scenároch.Predstavte si generovanie stimulu ako na stanovenie testovacieho scenára v laboratóriu.Rovnako ako vedci starostlivo kontrolujú podmienky pri pozorovaní chemických reakcií, digitálni dizajnéri remeselníci presné vstupy dodržiavajú, ako systém reaguje.

Overovanie výstupu

Overenie výstupu je proces kontroly, či sa skutočné výstupy systému zhodujú s očakávanými výsledkami.Tento krok je rozhodujúci pri chytení chýb skoro predtým, ako sa vyvinú do väčších problémov.Iní používajú overenie výstupu na potvrdenie, že systém spĺňa svoju zamýšľanú funkčnosť a vykonáva dôsledne za rôznych podmienok.Overenie výstupu zahŕňa automatizované aj ručné kontroly.Napríklad:

• Automatizované overovacie nástroje: Nástroje ako modely a Quartus umožňujú automatizované testovanie, kde sa výstupy systému porovnávajú s očakávanými výsledkami.Tým sa zrýchľuje proces overovania a znižuje chybu.

• Manuálne overenie (voliteľné): Pre zložitejšie scenáre môžu byť potrebné manuálne kontroly, aby sa zabezpečilo, že sú zakryté konkrétne hrany.

Nástroje a techniky na implementáciu testov

Kvartus: simulácia vizuálneho vstupu/výstupu

Quartus poskytuje grafické rozhranie, ktoré vizuálne usporiada vstupy a sleduje výstupy.Táto metóda môže byť prospešná pre začiatočníkov alebo pre systémy, ktoré si vyžadujú praktickejší vizuálny prístup.Tým, že Quartus umožňuje interakciu so simuláciou prostredníctvom grafického prostredia, pomáha demystifikovať vzťah medzi vstupmi a výstupmi, čo uľahčuje pochopenie toho, ako sa digitálny systém správa včas.Jednou z kľúčových silných stránok kvartu je, že je ideálny pre začiatočníkov.Jeho intuitívne vizuálne rozhranie poskytuje priamy spôsob, ako zistiť, ako vstupy ovplyvňujú výstupy bez potreby rozsiahlych znalostí skriptovania alebo programovania.Spätná väzba, ktorú ponúka, pomáha ľahšie pochopiť správanie obvodov, vďaka čomu je užitočným nástrojom pre nových digitálnych systémov.Kvartus však má svoje obmedzenia.Nastavenie simulácií v kvartách môže byť časovo náročné, najmä pre zložitejšie vzory.Tento nástroj je v porovnaní so simulačnými nástrojmi založený na skriptovaní menej flexibilný, ktoré môžu ponúknuť viac možností prispôsobenia a automatizácie.Pri práci na rozsiahlych alebo vysoko podrobných systémoch môže tento nedostatok flexibility predstavovať výzvu.

ModelsIm: Simulácia založená na texte pomocou skriptovania

ModelsIm zaujme iný prístup k simulácii uprednostňovaním textových vstupov prostredníctvom skriptovania.Vytvorte testovacie scenáre pomocou skriptov Verilog (.v) alebo VHDL (.vhd), namiesto vizuálneho usporiadania vstupov a výstupov.Táto metóda poskytuje presnosť a kontrolu.Namiesto spoliehania sa na grafické rozhranie definujete, ako by sa mal systém testovať prostredníctvom podrobných skriptov, čo umožňuje väčšie prispôsobenie a automatizáciu v procese simulácie.Jednou z kľúčových silných stránok modelov je flexibilita, ktorú ponúka.Použitím skriptov máte väčšiu kontrolu nad testovacími scenármi, ktoré im umožňujú vytvárať zložité a presné simulácie.Akonáhle je dizajnér oboznámený so syntaxou a pracovným tokom, nastavenie simulácií môže byť oveľa rýchlejšie v porovnaní s použitím grafických nástrojov, ako je Quartus.Schopnosť opätovného použitia a úpravy skriptov tiež zvyšuje jeho efektívnosť, najmä vo väčších projektoch.Textový prístup Modelsim však má s určitými obmedzeniami.Vyžaduje si solídne porozumenie syntaxe Verilog alebo VHDL, ktorá môže predstavovať výzvu pre začiatočníkov, ktorí nie sú oboznámení s jazykmi hardvéru.Výsledkom je, že Modelsim má strmšiu krivku učenia v porovnaní s viacerými nástrojmi vizuálnej simulácie.Novými používatelia môžu byť ťažké začať, ale s praxou sa presnosť a flexibilita ponúkajú skriptovaním stať cenným prínosom.

Preklenutá teória a prax pri overení

Testbenches slúžia ako most medzi teoretickými návrhmi a aplikáciami simuláciou toho, ako sa bude digitálny systém správať za rôznych podmienok vrátane okrajových prípadov a neočakávaných vstupov.V digitálnom dizajne je často ťažké predpovedať, ako bude systém fungovať v praxi založený výlučne na teoretických modeloch.Testbenches zatvára túto medzeru tým, že vám umožní posunúť sa nad rámec abstraktných konceptov dizajnu a vyhodnotiť správanie systému v kontrolovanom simulovanom prostredí.Jednou z kľúčových výhod používania simulačných nástrojov v testovacích zariadeniach je okamžitá spätná väzba, ktorú poskytujú počas ladenia.Nástroje, ako je Multisim alebo ModelsIM, ponúkajú vizuálne znázornenie správania systému a ukazujú, ako zmeny vo vstupoch v priebehu času ovplyvňujú výstupy.Táto spätná väzba vám umožňuje určiť problémy rýchlejšie, sledovať chyby späť k ich hlavnej príčine a podľa toho upraviť ich návrhy.Napríklad, ak systém nespĺňa obmedzenia načasovania alebo vykazuje neočakávané správanie v určitých vstupných sekvenciách, testbench môže tieto nedostatky okamžite zvýrazniť, dlho predtým, ako je systém fyzicky zostavený.Identifikáciou problémov na začiatku návrhu cyklu, testybenches znižuje potrebu nákladnej prepracovania a fyzického prototypovania, čím zefektívňuje proces overovania.Táto validácia v počiatočnom štádiu pomáha zabezpečiť, aby boli digitálne systémy funkčne správne a odolné voči podmienkam, čo ich robí spoľahlivejšími a znižuje riziko zlyhania po nasadení.Týmto spôsobom Testbenches pôsobia ako praktický nástroj na transformáciu teoretických návrhov na robustné.

Pokročilá architektúra Testbench

Pokročilé testovacie testy idú nad rámec jednoduchého testovania vstupu a výstupu začlenením ďalších komponentov na správu komplexných systémov.Štandardný testbench obsahuje tri kľúčové časti: a Stimul na vytvorenie vstupných signálov, a Dizajn testu (DUT), čo je skutočný testovaný hardvér a Monitor výstupu To kontroluje výstupy proti očakávaným výsledkom.Tieto komponenty spolupracujú na zabezpečení dôkladnejšieho a presnejšieho overenia digitálnych návrhov.

Zlepšenie presnosti TestBench zahŕňa použitie techník, ktoré zaisťujú, že návrh spoľahlivo vykonáva v rôznych scenároch. Náhodné testovanie Predstavuje nepredvídateľné vstupné vzory na overenie stability systému za rôznych podmienok. Testovanie na okraji Zameriava sa na hraničné situácie, keď sa systém s najväčšou pravdepodobnosťou stretne s chybami.Nakoniec, Regresné testovanie Zahŕňa opätovné spustenie testov po zmenách, aby sa potvrdilo, že neboli zavedené žiadne nové problémy, čo zabezpečuje, že systém zostáva v priebehu času konzistentný a bezchybný.

Skriptingové testy

Ak chcete vytvoriť efektívne a spoľahlivé testovacie hodnoty vo Verilog alebo VHDL, postupujte podľa kľúčových osvedčených postupov.Začnite jednoduché, potom sa najskôr rozbaľte testovaním základnej funkcie a postupne pridávajte zložitejšie scenáre.Použite komentáre a dokumentáciu, aby ste uľahčili porozumenie a údržbu skriptov jasným vysvetlením každej sekcie.Nakoniec automatizujte, kde je to možné, aby sa ušetril čas a znížil chyby pomocou slučiek a funkcií na spracovanie opakujúcich sa úloh a vstupných vzorov.

O nás

ALLELCO LIMITED

Čítaj viac

Rýchly dopyt

Zašlite prosím dotaz, okamžite odpovieme.

Digitálna fázová slučka (DPLL): dizajn, komponenty a operácie

na 2025/01/7

Vývoj a vplyv architektúry RISC na moderné výpočty

na 2025/01/7

Populárne príspevky

-

Komplexné súpravy inštrukcií: Ako zmenili výpočty?

na 8000/04/17 147713

-

USB-C Pinout a funkcie

na 2000/04/17 111727

-

Pomocou Xilinx Unified Simulation Primitive: Komplexný sprievodca dizajnom a simuláciou FPGA

na 1600/04/17 111322

-

Napájacie napätia v elektronike: Význam VCC, VDD, VEE, VSS a GND

na 0400/04/17 83609

-

Sprievodca konektorom RJ45: Pinout, kábly, typy káblov a použitia

na 1970/01/1 79262

-

Konečný sprievodca k farebným kódom drôtu v moderných elektrických systémoch

Spôsob, akým naše elektrické systémy používajú farby, nie je len pre vzhľad.Každá farba drôtu teraz označuje špecifickú funkciu, čo uľahčuje správne identifikáciu a spracovanie elektrických kompone...na 1970/01/1 66777

-

Kvalita (Q) Faktor: Rovnice a aplikácie

Faktor kvality alebo „Q“ je dôležitý pri kontrole, ako dobre induktory a rezonátory pracujú v elektronických systémoch, ktoré používajú rádiové frekvencie (RF).'Q' meria, ako dobre obvod minimalizu...na 1970/01/1 62946

-

Sprievodca čistením ventilu: funkcia, príznaky, testovanie a výmena za optimálny výkon motora

Čistý ventil je kľúčovou súčasťou systému automobilu, ktorý pomáha udržiavať vzduch čistý riadením výparov paliva skôr, ako môžu uniknúť do atmosféry.To nielen pomáha životnému prostrediu znížením ...na 1970/01/1 62826

-

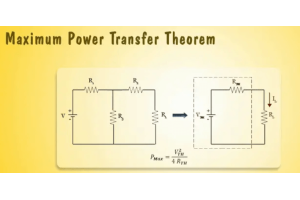

Dosiahnutie maximálneho výkonu s maximálnou vetou prenosu energie

Maximálna veta prenosu energie vysvetľuje, ako energia zo zdroja, napríklad batéria alebo generátor, tečie na pripojené zaťaženie.Zobrazuje presnú podmienku, keď zaťaženie prijíma najviac energie.T...na 1970/01/1 54028

-

Špecifikácie batérie A23 a kompatibilita

Batéria A23 je malá batéria v tvare valca s vysokým napätím.Nazýva sa tiež 23A, 23ae alebo MN21, beží na 12 voltoch a oveľa vyšších ako batérie AA alebo AAA.Vďaka jeho špeciálnemu dizajnu ...na 1970/01/1 51989