CPLD vysvetlil: Sprievodca programovateľnými logickými zariadeniami

V dynamickom svete elektronického dizajnu vynikajú komplexné programovateľné logické zariadenia (CPLDS) ako všestranné nástroje, bezproblémovo miešanie prispôsobivosti, presnosti a efektívnosti.Tieto zariadenia revolúcia v návrhu obvodu zavedením programovateľných makro buniek a dominantnej prepojenej matrice, čo umožňuje vytváranie zložitých logických funkcií s pozoruhodnou spoľahlivosťou.Od svojho vzniku v 80. rokoch po ich kľúčovú úlohu v moderných odvetviach, ako sú siete, automobilový priemysel a letectvo, CPLDS sa ukázali ako potrebné pre hľadanie flexibility a výkonu.Tento článok sa venuje ceste CPLDS, ich charakteristických funkcií, praktických aplikácií a programovacích metodík, vďaka ktorým sú základným kameňom digitálnej logiky.Katalóg

Prehľad CPLD

V rámci Dominionu komplexných programovateľných logických zariadení (CPLDS) jeden objaví sofistikovanú tapisériu programovateľných logických makro buniek, ktoré sú prepletené dominantnou prepojenou matricou.Tieto riadky jednotiek makro bunky (MC) a vstupných/výstupných (I/O) vám umožňujú obratne navrhovať obvody a konfigurovať štruktúry pre jedinečné funkcie.Na rozdiel od zariadení, ktoré sú zmätené ich zložitým načasovaním prepojenia, CPLDS využívajú nehnuteľné kovové drôty.Táto charakteristika im udeľuje konzistentné a predvídateľné správanie hodín, vďaka čomu sú predpovede načasovania spoľahlivejšie a presnejšie.

Cesta a využitie

V 70. rokoch 20. storočia ohlasoval príchod programovateľných logických zariadení (PLDS), čím podporoval presun smerom k programovateľným makro jednotkám.Tento posun predstavil dostatočnú flexibilitu dizajnu a odlišoval ich od statických digitálnych obvodov, hoci ich užitočnosť bola spočiatku obmedzená na jednoduchšie obvody.Príchod CPLDS v polovici osemdesiatych rokov revolúciou v tejto krajine revolúciou v tejto krajine a vydláždil cestu pre zložité návrhy obvodov.Odvtedy sa prepojili do štruktúry priemyselných odvetví, ako sú sietia, automobilová elektronika, obrábanie CNC a letecké systémy.Môžete si spomínať na spôsob, akým CPLDS zjednodušili procesy, ktoré kedysi požadovali dôkladnú manuálnu prácu, čím sa označuje pozoruhodný skok v efektívnosti.

Výrazné vlastnosti CPLDS

CPLD sa rozlišujú prostredníctvom svojho prispôsobivého programovania, rozsiahlej integrácie, rýchlych rozvojových schopností a rozsiahlej uplatniteľnosti spolu s ekonomickými výrobnými nákladmi.Oslovujú tých, ktorí majú minimálne skúsenosti s hardvérom, slúžia ako spoľahlivé a bezpečné výrobky, ktoré si nevyžadujú vyčerpávajúce testovanie.Ako dôkaz svojej zdatnosti vo veľkých dizajnoch obvodov zohrávajú CPLD kľúčovú úlohu pri vývoji prototypov a podávajú sa pod 10 000 jednotiek, ktoré pre vás stelesňujú užitočnú kompetenciu.Adept, s ktorou sa CPLD prispôsobujú rozvíjajúcim sa požiadavkám projektu, často im prináša ocenenie a zdôrazňuje ich skutočnú všestrannosť v dynamických prostrediach.

Aplikačné metódy

Tieto integrované obvody vám umožňujú rozpracovať logické funkcie prispôsobené ich potrebám pomocou jazykov schémy aj hardvéru na vývojových platformách.Napríklad pri navrhovaní odpovediaceho stroja sa pripravujú a zostavujú opisy hardvéru a hardvérové popisy.Pri využívaní kábla sťahovania sa kód prenesie do CPLD na programovanie v systéme, ktorý obsahuje testovanie, riešenie problémov a vylepšovanie návrhov.Úspešne vypracované vzory sa potom hromadne vyrábajú replikáciou čipov CPLD.V projektoch, ako sú systémy semaforu, sa opakovanie procesu navrhovania stáva potrebným, podobne ako prestavba domu na obnovenie jeho novosti.Táto opakujúca sa metodika často kladie základy na zvládnutie, zvyšovanie zručností a dôvery.

Vedúce varianty

V priebehu rokov predstavili spoločnosti ako Altera, Mretice a Xilinx významné línie CPLDS.Pozoruhodné príklady zahŕňajú Altera's EPM7128S, Mrežová LC4128Va Xilinx's XC95108 .Tieto modely našli významnú úlohu v rôznych globálnych aplikáciách.Tí, ktorí mali tú česť pracovať s týmito odlišnými výrobkami, často poznamenávajú jemné, ale silné rozdiely, ktoré optimalizujú konkrétne funkcie.Odráža to jemný výberový proces ovplyvnený konkrétnymi požiadavkami na projekt, kde každý variant má jedinečnú príťažlivosť.

Identifikácia a klasifikácia FPGA a CPLD

|

Aspekt |

Cpld |

FPGA |

|

Tvorba logického správania |

Vytvorte logické správanie pomocou štruktúry termínu produktu.

Príklady: Séria mriežky IsplSi, Xilinx XC9500 Series, Altera MAX7000S

Séria, séria mriežky Mach |

Vytvorte logické správanie pomocou metódy vyhľadávania tabuľky.

Príklady: Xilinx Spartan Series, Altera Flex10k, séria ACEX1K |

|

Vhodnosť |

Vhodné pre algoritmy a kombináciu logiky, diela

Lepšie s obmedzenými spúšťačmi a pojmami bohatých produktov |

Vhodný pre sekvenčnú logiku, funguje lepšie s

štruktúry bohaté na spúšťače |

|

Oneskorenie načasovania |

Konštrukcia nepretržitého zapojenia poskytuje rovnomerné a

predvídateľné oneskorenia načasovania |

Segmentovaná štruktúra zapojenia vedie k nepredvídateľnému načasovaniu

oneskorenie |

|

Flexibilita programovania |

Pevné vnútorné obvody sú upravené na programovanie.

Používa sa programovanie na úrovni logických blokov |

Interné zapojenie je upravené pre programovanie.Logika

Programovanie na úrovni brány umožňuje väčšiu flexibilitu |

|

Integrácia |

Nižšia integrácia v porovnaní s FPGA |

Vyššia integrácia s komplexnejšou štruktúrou zapojenia a

logická implementácia |

|

Ľahké použitie |

Ľahšie sa používa s programovaním prostredníctvom E2PROM alebo FastFlash.

Nevyžaduje sa žiadny externý pamäťový čip |

Na ukladanie programovania vyžaduje externú pamäť

informácie, ktoré vedú k zložitejšiemu použitiu |

|

Rýchlosť a predvídateľnosť |

Rýchlejšia rýchlosť a lepšie načasovanie predvídateľnosti v dôsledku

premietané prepojenie medzi logickými blokmi |

Pomalšia rýchlosť a menej predvídateľné načasovanie v dôsledku

Programovanie na úrovni brány a distribuované prepojenie |

|

Programovanie |

Používa programovanie E2Prom alebo Flash Memory.Programovanie

je zachovaný, keď je systém vypnutý.Podporuje programovanie na a

programátor alebo v systéme |

Na základe programovania SRAM.Programovacie údaje sa strácajú, keď

Systém je vypnutý a musí byť načítaný.Podporuje dynamickú

konfigurácia |

|

Dôvernosť |

Ponúka lepšiu dôvernosť |

Poskytuje nižšiu dôvernosť |

|

Spotreba energie |

Vo všeobecnosti vyššia spotreba energie, najmä s

vyššia integrácia |

Nižšia spotreba energie v porovnaní s CPLD |

Programovacie jazyky CPLD

Analýza, ako sú naprogramované komplexné programovateľné logické zariadenia (CPLDS), je základným kameňom pri tvorbe všestranných hardvérových riešení.Historické metódy programovania CPLD sa spoliehali na rebríky alebo hardvérové popisy jazyky (HDL), pričom prevládajúcimi rozhodnutiami sú Verilog HDL a VHDL.Vybraný jazyk môže formovať stratégiu dizajnu a prevádzkovú efektívnosť implementácií.

• Verilog HDL: Verilog HDL je vážená pre svoju jednoduchú syntax a robustné simulačné schopnosti, čo odráža metodiky použité pri digitálnej logike.Jeho integrácia s nástrojmi Electronic Design Automation (EDA) vám umožňuje plynulo vykonávať syntézu a simuláciu.Zistila sa, že syntax Verilogu podobnej C znižuje bariéru vstupu pre tých, ktorí majú programovacie prostredie, urýchľujú cestu od dizajnu k nasadeniu v širokom spektre priemyselných sektorov.

• Vhdl: VHDL poskytuje komplikovanejšiu a výraznejšiu možnosť pre programovanie HDL.Je to často voľba pre projekty, ktoré požadujú dôkladnú dokumentáciu a prísnu kontrolu typu, vlastnosti hodnotené v leteckom a obrannom priemysle.Môžete si uvedomiť, že napriek potenciálnej zložitosti VHDL v menších projektoch jej disciplinovaná štruktúra podporuje vytváranie mimoriadne spoľahlivých návrhov, čo je nevyhnutnosť v prostrediach, v ktorých dominuje bezpečnosť.

O nás

ALLELCO LIMITED

Čítaj viac

Rýchly dopyt

Zašlite prosím dotaz, okamžite odpovieme.

Tranzistory NMOS: návrh, prevádzka a aplikácie

na 2024/12/29

Fast Fourierov transformácia (FFT): Revolucionalizovanie spracovania digitálneho signálu

na 2024/12/29

Populárne príspevky

-

Komplexné súpravy inštrukcií: Ako zmenili výpočty?

na 8000/04/18 147778

-

USB-C Pinout a funkcie

na 2000/04/18 112035

-

Pomocou Xilinx Unified Simulation Primitive: Komplexný sprievodca dizajnom a simuláciou FPGA

na 1600/04/18 111352

-

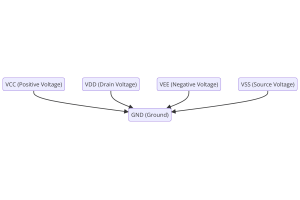

Napájacie napätia v elektronike: Význam VCC, VDD, VEE, VSS a GND

na 0400/04/18 83794

-

Sprievodca konektorom RJ45: Pinout, kábly, typy káblov a použitia

na 1970/01/1 79602

-

Konečný sprievodca k farebným kódom drôtu v moderných elektrických systémoch

Spôsob, akým naše elektrické systémy používajú farby, nie je len pre vzhľad.Každá farba drôtu teraz označuje špecifickú funkciu, čo uľahčuje správne identifikáciu a spracovanie elektrických kompone...na 1970/01/1 66976

-

Sprievodca čistením ventilu: funkcia, príznaky, testovanie a výmena za optimálny výkon motora

Čistý ventil je kľúčovou súčasťou systému automobilu, ktorý pomáha udržiavať vzduch čistý riadením výparov paliva skôr, ako môžu uniknúť do atmosféry.To nielen pomáha životnému prostrediu znížením ...na 1970/01/1 63111

-

Kvalita (Q) Faktor: Rovnice a aplikácie

Faktor kvality alebo „Q“ je dôležitý pri kontrole, ako dobre induktory a rezonátory pracujú v elektronických systémoch, ktoré používajú rádiové frekvencie (RF).'Q' meria, ako dobre obvod minimalizu...na 1970/01/1 63044

-

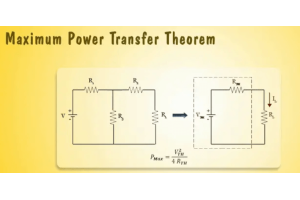

Dosiahnutie maximálneho výkonu s maximálnou vetou prenosu energie

Maximálna veta prenosu energie vysvetľuje, ako energia zo zdroja, napríklad batéria alebo generátor, tečie na pripojené zaťaženie.Zobrazuje presnú podmienku, keď zaťaženie prijíma najviac energie.T...na 1970/01/1 54097

-

Špecifikácie batérie A23 a kompatibilita

Batéria A23 je malá batéria v tvare valca s vysokým napätím.Nazýva sa tiež 23A, 23ae alebo MN21, beží na 12 voltoch a oveľa vyšších ako batérie AA alebo AAA.Vďaka jeho špeciálnemu dizajnu ...na 1970/01/1 52198